SR-TE Optimization

You can use the SR-TE Optimization tool to design, capacity plan, and manually configure networks to meet the following objectives:

Note |

SR-TE Optimization tool supports both Inter-Area and Inter-AS functionalities. |

-

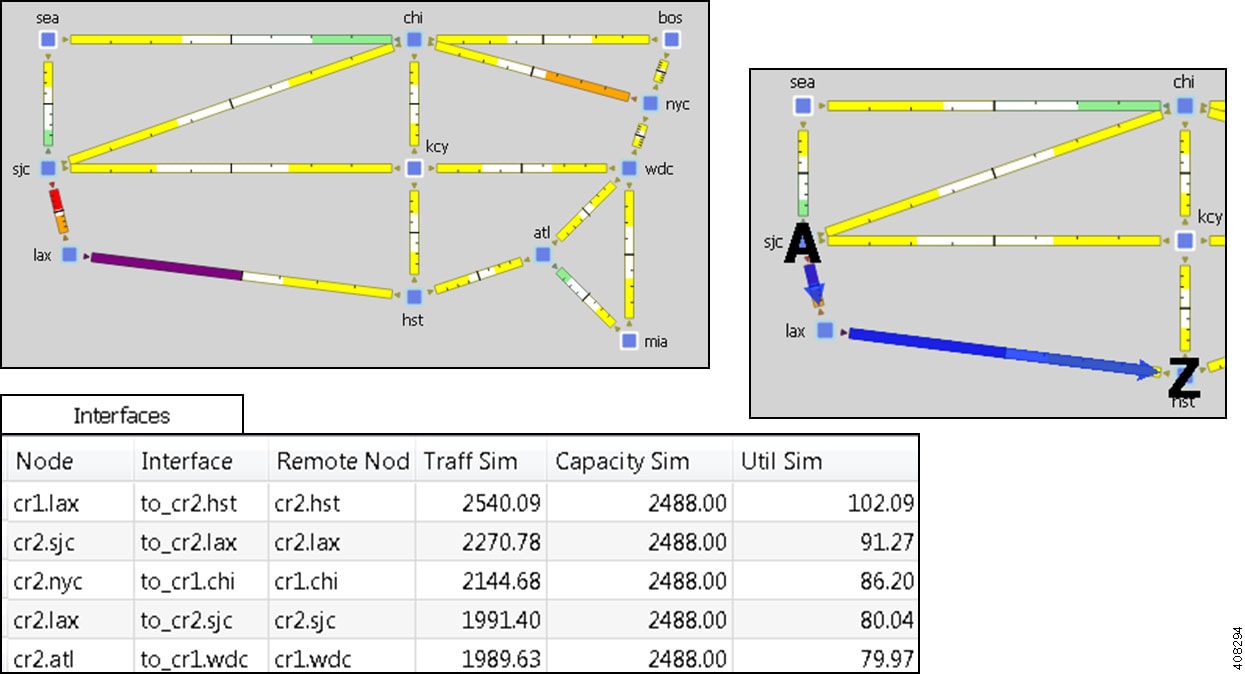

TE Metric or Delay Minimization—Minimize distance between hops with respect to metrics other than IGP metrics. These can be either TE metrics configured on interfaces (which can be set proportional to circuit latency) or latencies (delays) for each circuit. An example application is a differentiated service in which latency-sensitive network traffic is routed on shortest latency paths, while the bulk of the traffic routes over cost-optimized paths.

-

Avoidance—Create or optimize segment lists so they avoid routing through specified objects (nodes, interfaces, L1 links, L1 nodes, or SRLGs). An example application is routing pairs of LSPs, each over a different plane in a dual-plane network. The same traffic is routed over both LSPs simultaneously, thus improving availability.

While there is an option to specify a maximum number of hops, doing so might not achieve the lowest possible latency. In this case, the best achievable solution is provided.

You can additionally avoid unnecessary LSP churn by specifying boundaries (bounds) on the path length and margins within which the shortest path must be optimized.

Note

Unless qualified with “TE” or “IGP,” the term metric in this chapter applies to IGP metric, TE metric, or delay.

Optimizing SR-TE LSPs

Choose Tools > SR LSP Optimization > SR-TE Opt. Then identify which SR LSPs to optimize: all SR LSPs, those selected before opening the dialog box, or those with specific tags. The default is to optimize all selected SR LSPs, and by default, all SR LSPs are considered selected.

-

Parameters for optimizing explicit LSP paths are specified in the Bound, Margin, and Constraints areas of the dialog box. If you do not specify a bound, margin, or constraint, WAE Design generates the best possible SR LSP routes for the given path metric.

-

A segment list is created or updated for all SR LSP paths that can be optimized using the minimum number of segment list hops possible.

-

If an LSP has a directly associated segment list, the segment list is deleted.

-

If an LSP has no LSP paths, an LSP path with a path option of 1 is created.

-

If an LSP has no segment list, but it has LSP paths, a segment list is created for the active path if it exists and if not, for the lowest path option (where lowest means the smallest value).

-

If an LSP has associated LSP paths and a segment list associated with either the active path or lowest path option, the segment list hops in the segment list are updated.

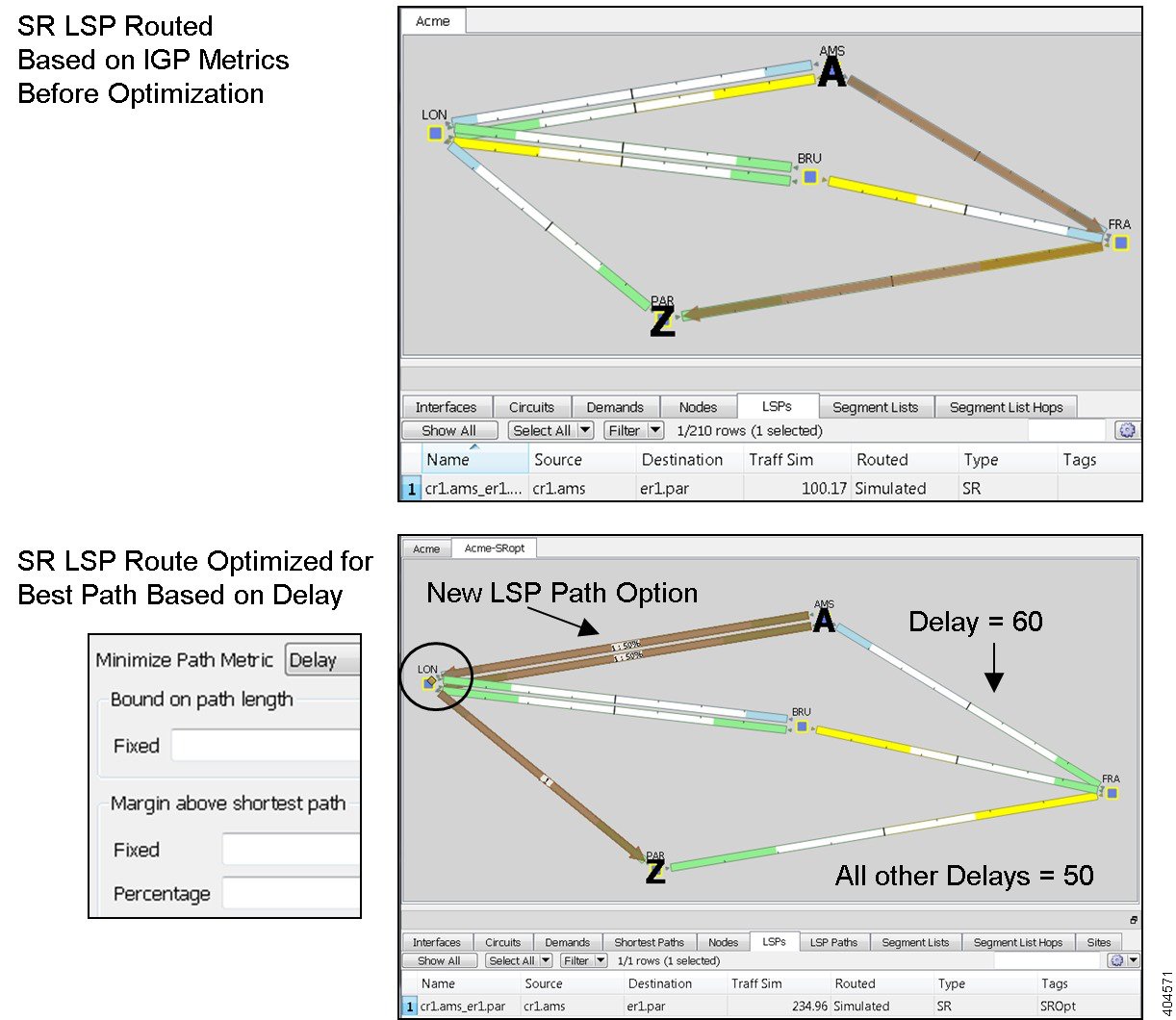

Example: Example SR LSP Optimization shows an SR LSP that normally routes from AMS-FRA-PAR based on IGP metrics. It has no LSP paths. All circuits have a Delay Sim value of 50 except for the AMS-FRA circuit, which has a Delay Sim value of 60. Optimizing this SR LSP based on delay results in rerouting the SR LSP over the shortest achievable delay path, creating an LSP path with a path option of 1, and creating a segment list node hop on the cr.lon node.

-

-

The final hop is either a node hop or interface whose remote node is the destination of the LSP.

-

If it is not possible to achieve the lowest possible path without exceeding the specified maximum number of segment list hops, WAE Design provides the best achievable solution within this restriction of maximum permissible hops.

-

If it is not possible to avoid all specified nodes for an SR LSP, that SR LSP is not updated.

-

If an existing segment list would be better optimized by removing all segment list hops, those hops are removed, though the segment list remains.

-

If a previously optimized SR LSP does not need further optimization, it is not changed and its previously set SROpt tag is removed.

-

If the source and destination nodes are in different IGP areas, WAE Design creates an explicit hop on the most optimal ABR for each IGP area that the SR LSP traverses.

Figure 1. Example SR LSP Optimization

Optimizing the Path Metric

The Minimize Path Metric selection defines whether to optimize SR LSPs based on interface IGP metrics, interface TE metrics, or circuit delays. This minimization is for the sum of the metrics along the path. Note that for inter-AS SR LSPs, these metrics are calculated end-to-end for the LSP, not per AS. These properties are configurable from an interface Properties dialog box, and delays can also be set in a circuit Properties dialog box.

Bound and Margin

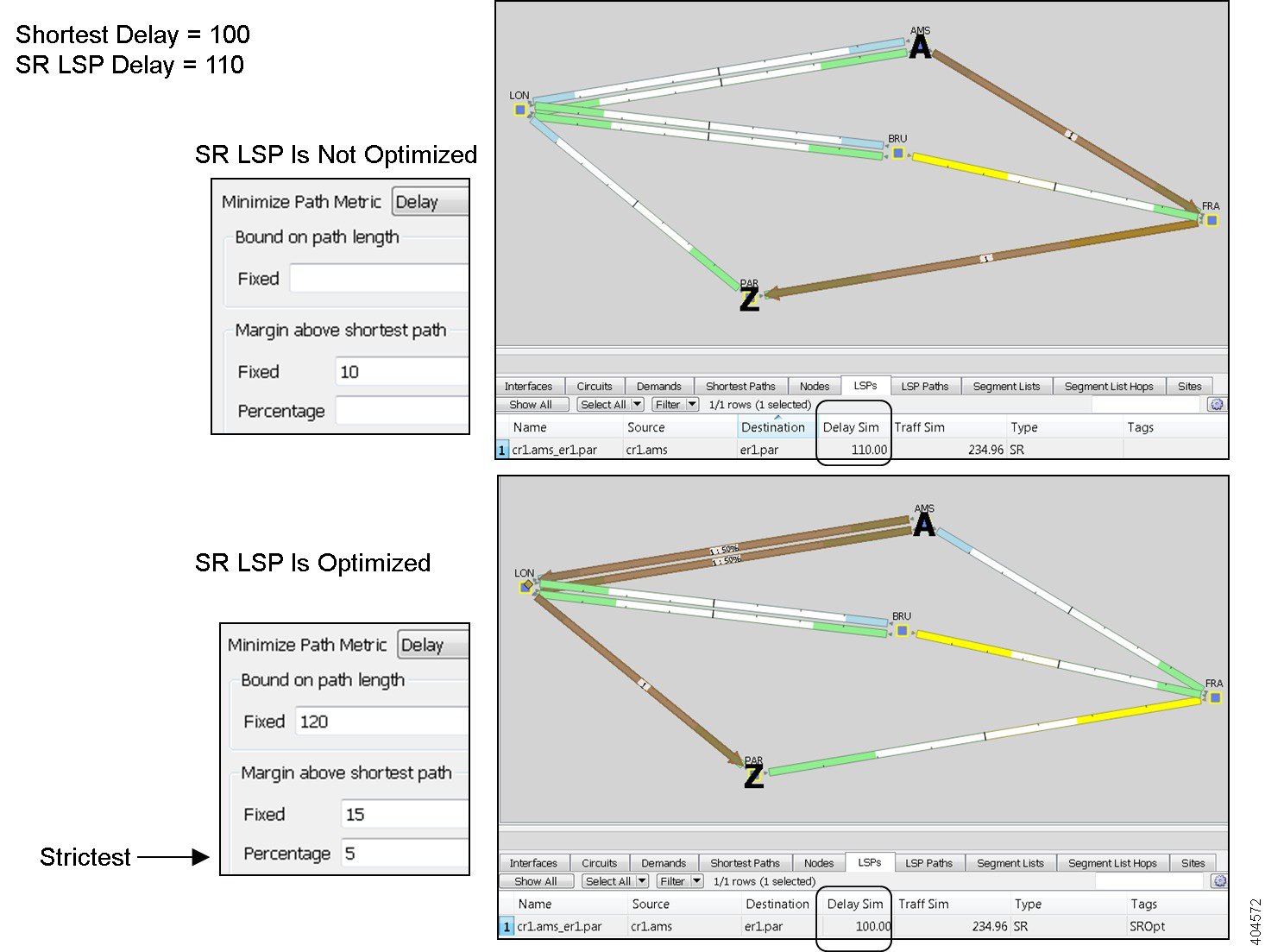

Bounds and margins identify which paths to optimize, as well as when to stop optimizing a given path. If you enter a value for more than one restriction, WAE Design uses the strictest limitation as the optimization target. If there is no bound or margin specified, WAE Design optimizes LSP paths to the best possible solution (lowest total metrics for the LSP path).

Bound: Maximum Acceptable Path Length

The Fixed Bound entry lets you set the maximum path metric that is acceptable. WAE Design tries to optimize LSP paths with metrics that exceed this bound. If a solution adhering to this bound cannot be found, the best possible solution is provided and bound violations are listed in the report. LSP paths that are less than or equal to this bound are not optimized.

Example: If you select to optimize LSP paths based on TE metrics, the value entered is 50, and the sum of TE metrics on the LSP path is 51, that LSP path is optimized.

Enter a number based on the selected path metric. A TE metric is a property values whose total sum for the LSP path cannot be exceeded. The delay is also a property value, but it is in milliseconds (ms). If you enter “50” and you have selected delay as the metric to optimize, this represents 50 ms as the maximum acceptable delay for the LSP path.

Margin: Maximum Acceptable Metric Above Shortest Path

The Margin entries let you identify the acceptable deviation above the shortest achievable path metric. Any existing LSP path with a metric that is less than or equal to the shortest path metric plus the margin is not optimized.

-

Fixed—The amount by which a metric must be surpassed before it is optimized.

Example: If an SR LSP route has a delay of 110 (as in Example SR LSP Optimization), a fixed margin set to 10, and the shortest achievable delay path is 100, the current SR LSP is within the margin and will not be updated (Example SR LSPs Optimized with Margins). If the fixed margin is set to 9, the SR LSP would be optimized.

100 (shortest path) + 10 (fixed margin) = 110, so all paths greater than 110 are optimized

-

Percentage—The amount by which a metric must be surpassed, expressed as a percentage of the shortest path, before it is optimized.

Example: If an existing SR LSP route has a TE metric of 210, a percentage margin set to 10%, and the shortest achievable TE metric path is 200, the current SR LSP is within the margin and will not be updated. If the current SR LSP had a metric of 225, it would be optimized.

200 (shortest path) x .10 (percentage margin) = 20, so all paths greater than 220 must be optimized

Example: If an SR LSP route has a delay of 110 (as in Example SR LSP Optimization), a fixed bound is set to 120, a fixed margin is set to 15, a percentage margin is set to 5%, and the shortest achievable delay path is 100, the strictest of these restrictions takes precedence, and the SR LSP is optimized (Example SR LSPs Optimized with Margins).

Fixed Bound = 120

100 (shortest path) + 15 (fixed margin) = 115

100 (shortest path) x .05 (percentage margin) = 5, so all paths greater than 105 are optimized because it is the strictest margin

Figure 2. Example SR LSPs Optimized with Margins

Constraints

The constraints let you specify restrictions for the optimizations.

-

Maximum Segment List Hops—The maximum number of segment list hops that any given segment list can contain after optimization. If no value is specified, WAE Design creates as many hops as needed to optimize the SR LSP.

-

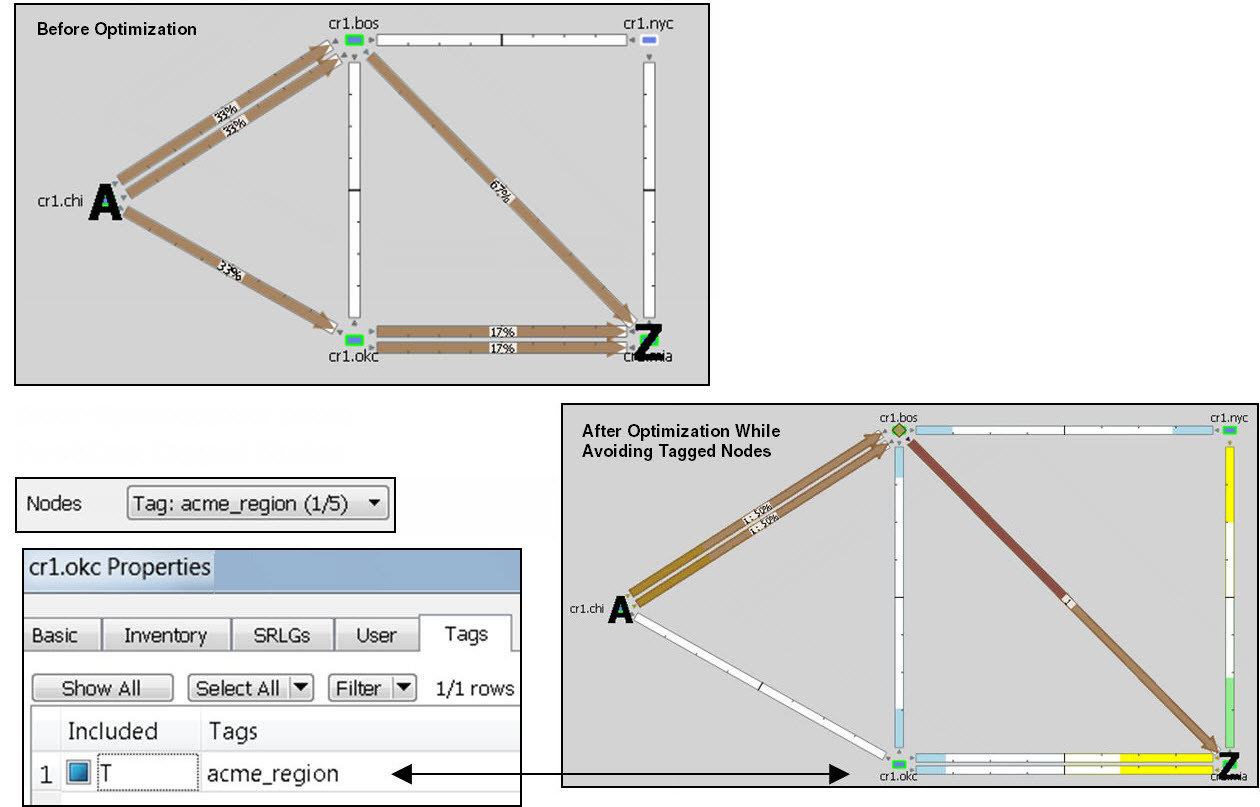

Avoid—Do not permit optimized segment lists to route through the selected or tagged objects (nodes, interfaces, L1 links, L1 nodes, or SRLGs). This constraint is useful when modeling dual-plane topologies that route disjoint LSPs.

Example: Example of Avoiding Tagged Nodes During SR-TE Optimization shows an SR LSP from cr1.chi to cr1.mia that is routed based on its shortest IGP route. It also shows the optimized SR LSP path if it were to avoid cr1.okc based on its tag.

-

Restrict segment nodes to core nodes—Segment list node hops must be core nodes (nodes that have their Function property set to “core”), and the local node of segment list interface hops must be a core node. An SR LSP could still route using edge nodes if they are not used as hops.

Figure 3. Example of Avoiding Tagged Nodes During SR-TE Optimization

Using SR Tags and Creating New Plan Files

These options identify how optimized SR LSPs are tagged, and whether to create new plan files with the results:

-

Tag updated LSPs with—Create and add tags to all SR LSPs rerouted during optimization. Using tags makes it easier to find the changed SR LSPs that are deployed to the network or to find those SR LSPs that need to be reconfigured in the actual network according to the optimization results. By default, newly optimized LSPs are tagged as SROpt .

-

New plan for result—This default option creates a new plan with the results of the optimization. Unless a name is specified, WAE Design attaches an -SRopt suffix to the current plan filename. If not selected, WAE Design changes the current plan file with the updated information. Saving this plan file then simplifies the process of identifying which LSPs to reconfigure in the network.

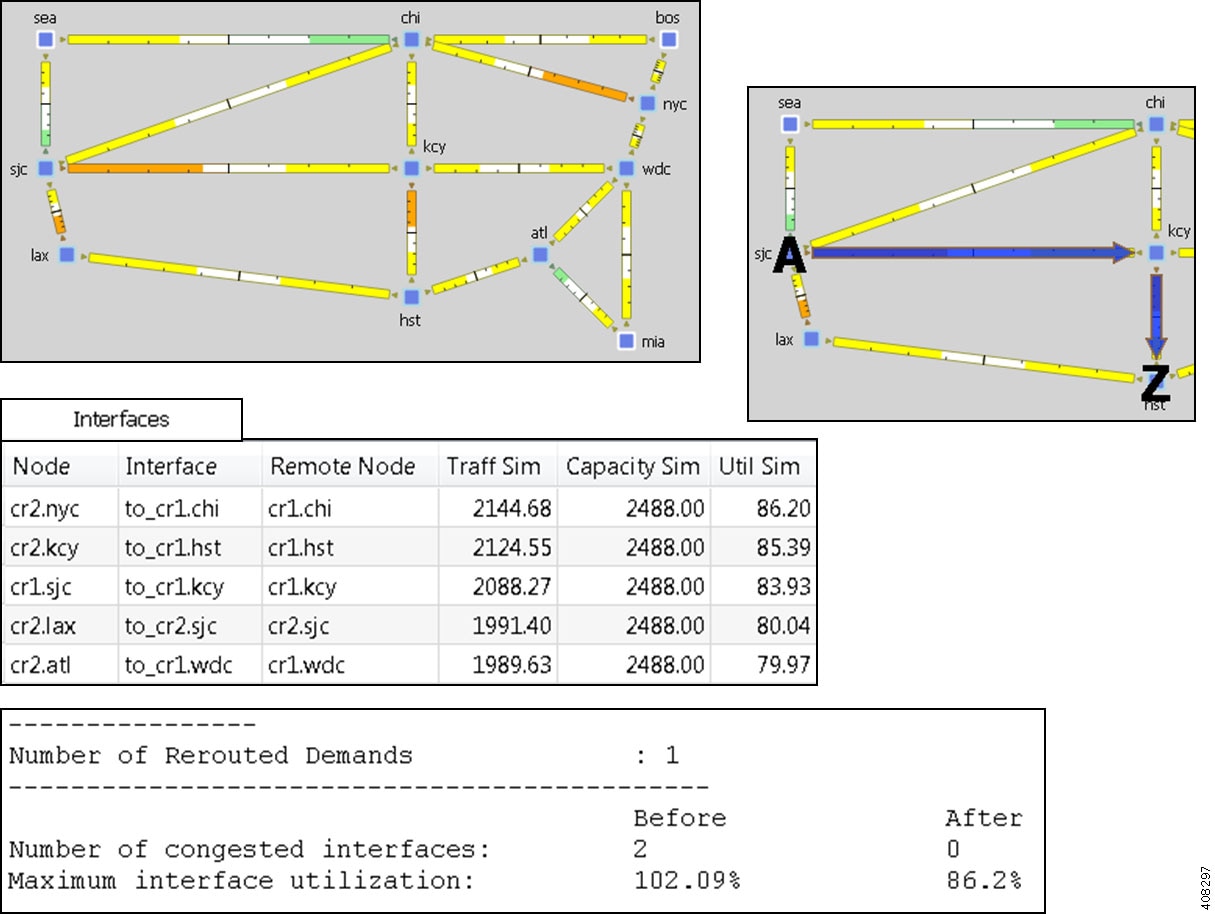

Optimization Report

Upon completion, WAE Design writes a report containing the results of the optimization, as well as verifications that the results met the criteria for avoiding nodes and meeting the specified bounds. To access this information later, choose Window > Reports.

Feedback

Feedback