Introducción al almacenamiento en cola en interfaces de Frame Relay del router

Contenido

Introducción

Este documento se ocupa de la arquitectura de espera jerárquica en las interfaces seriales que se han configurado con el encapsulado de Frame Relay. Cuando se configuran con Frame Relay Traffic Shaping (FRTS), las interfaces de Frame Relay soportan las siguientes capas en la cola:

-

Cola PVC

-

Cola de nivel de interfaz

Prerequisites

Requirements

Quienes lean este documento deben tener conocimiento de lo siguiente:

-

Cisco 2600, 3600 y 7200 Series Routers

Componentes Utilizados

Las configuraciones utilizadas en este documento se capturaron en un Cisco 7200 Series Router con el siguiente hardware y software:

-

Adaptador de puerto T1 multicanal PA-MC-4T1

-

Software Cisco IOS® versión 12.2(6)

La información que se presenta en este documento se originó a partir de dispositivos dentro de un ambiente de laboratorio específico. Todos los dispositivos que se utilizan en este documento se pusieron en funcionamiento con una configuración verificada (predeterminada). Si la red está funcionando, asegúrese de haber comprendido el impacto que puede tener un comando antes de ejecutarlo.

Convenciones

Para obtener más información sobre las convenciones del documento, consulte Convenciones de Consejos Técnicos de Cisco.

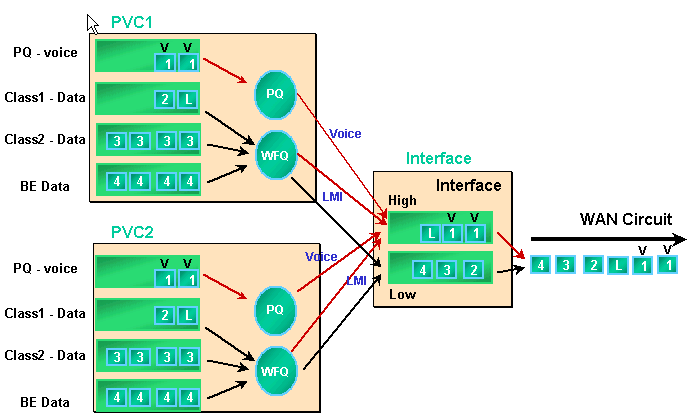

Capas de colas

La siguiente figura ilustra las dos capas de colas cuando se aplica FRTS a la interfaz. La aplicación de FRTS y los acuerdos de implementación del foro de Frame Relay (FRF.12) hace que la cola de nivel de interfaz cambie a la cola FIFO dual según las plataformas que soportan esta técnica de colocación en cola. Las dos colas incluyen una cola de alta prioridad para llevar voz en IP (VoIP) y ciertos paquetes de control y una cola de baja prioridad para llevar todos los demás paquetes. Para obtener más información sobre la colocación en cola FIFO dual, vea la sección FIFO dual.

Las interfaces Frame Relay admiten colas de interfaz así como colas PVC cuando se habilita la colocación en cola FRTS y PVC. Cada cola PVC también admite un sistema de cola equilibrada ponderada (WFQ) independiente, si la cola PVC está configurada como WFQ.

Cola PVC

Tanto las interfaces Frame Relay como las ATM pueden admitir varios circuitos virtuales (VC). Dependiendo del hardware, estas interfaces admiten colas PVC, lo que garantiza que un VC congestionado no consuma todos los recursos de memoria y afecte a otros VC (no congestionados).

El comando frame-relay traffic-shaping habilita el modelado de tráfico y la colocación en cola PVC para todos los VC en una interfaz Frame Relay. El modelado del tráfico PVC brinda mayor control sobre el flujo de tráfico en un VC individual. El modelado de tráfico combinado con colas VC limita el consumo del ancho de banda de la interfaz para un solo VC. Sin ningún modelado, un VC puede consumir todo el ancho de banda de la interfaz y matar de hambre a otros VC.

Si no se especifican valores de modelado, se aplican los valores predeterminados para la velocidad media y el tamaño de ráfaga. Cuando la carga ofrecida al VC excede los valores de modelado, los paquetes excedentes se almacenan en la cola de almacenamiento en buffer de paquetes del VC. Una vez que los paquetes se almacenan en la memoria intermedia, puede aplicar un mecanismo de colocación en cola y controlar eficazmente el orden de los paquetes quitados de la cola del VC a la cola de la interfaz. De forma predeterminada, las colas de PVC utilizan la colocación en cola en el orden de llegada con un límite de cola de 40 paquetes. Utilice el comando frame-relay holdq en el modo de configuración map-class para cambiar este valor. También puede aplicar colas de baja latencia (LLQ) o colas equitativas basadas en clases (CBWFQ) mediante una política de calidad de servicio (QoS) configurada con los comandos de la interfaz de línea de comandos (CLI) de QoS modular (MQC). Además, puede aplicar WFQ directamente dentro de map-class con el comando fair queue. Este comando configura al router para que clasifique el tráfico de acuerdo con el flujo y coloca estos flujos en sus propias subcolas. De esta forma, el comando fair queue crea un sistema WFQ por VC.

A continuación se describen los mecanismos de colocación en cola detallados para las colas PVC.

-

Ejecute el comando show frame-relay pvc 20. El identificador de conexión de enlace de datos (DLCI) de Frame Relay se identifica con el 20. El siguiente resultado no muestra información de colocación en cola porque FRTS no está habilitado.

Router# show frame PVC 20 PVC Statistics for interface Serial6/0:0 (Frame Relay DTE) DLCI = 20, DLCI USAGE = LOCAL, PVC STATUS = DELETED, INTERFACE = Serial6/0:0.1 input pkts 0 output pkts 0 in bytes 0 out bytes 0 dropped pkts 0 in FECN pkts 0 in BECN pkts 0 out FECN pkts 0 out BECN pkts 0 in DE pkts 0 out DE pkts 0 out bcast pkts 0 out bcast bytes 0 PVC create time 00:00:38, last time PVC status changed 00:00:25

-

Configure FRTS usando el comando frame-relay traffic-shaping en el modo de configuración de interfaz bajo la interfaz física. Ejecute de nuevo el comando show frame-relay PVC [dlci].

Router# show frame-relay PVC 20 PVC Statistics for interface Serial6/0:0 (Frame Relay DTE) DLCI = 20, DLCI USAGE = LOCAL, PVC STATUS = DELETED, INTERFACE = Serial6/0:0.1 input pkts 0 output pkts 0 in bytes 0 out bytes 0 dropped pkts 0 in FECN pkts 0 in BECN pkts 0 out FECN pkts 0 out BECN pkts 0 in DE pkts 0 out DE pkts 0 out bcast pkts 0 out bcast bytes 0 PVC create time 00:04:59, last time PVC status changed 00:04:46 cir 56000 bc 7000 be 0 byte limit 875 interval 125 !--- Shaping parameters. mincir 28000 byte increment 875 Adaptive Shaping none pkts 0 bytes 0 pkts delayed 0 bytes delayed 0 shaping inactive traffic shaping drops 0 Queueing strategy: fifo !--- Queue mechanism. Output queue 0/40, 0 drop, 0 dequeued !--- Queue size.

-

De forma predeterminada, las colas PVC utilizan un límite de cola de salida de 40 paquetes. Utilice el comando frame-relay holdq para configurar un valor no predeterminado.

Router(config)# map-class frame-relay shaping Router(config-map-class)# no frame-relay adaptive-shaping Router(config-map-class)# frame-relay holdq 50 Router(config)# interface serial 6/0:0.1 Router(config-subif)# frame-relay interface-dlci 20 %PVC is already defined Router(config-fr-dlci)# class shaping Router(config-fr-dlci)# end Router# sh frame PVC 20 PVC Statistics for interface Serial6/0:0 (Frame Relay DTE) DLCI = 20, DLCI USAGE = LOCAL, PVC STATUS = DELETED, INTERFACE = Serial6/0:0.1 input pkts 0 output pkts 0 in bytes 0 out bytes 0 dropped pkts 0 in FECN pkts 0 in BECN pkts 0 out FECN pkts 0 out BECN pkts 0 in DE pkts 0 out DE pkts 0 out bcast pkts 0 out bcast bytes 0 PVC create time 00:11:06, last time PVC status changed 00:10:53 cir 56000 BC 7000 be 0 byte limit 875 interval 125 mincir 28000 byte increment 875 Adaptive Shaping none pkts 0 bytes 0 pkts delayed 0 bytes delayed 0 shaping inactive traffic shaping drops 0 Queueing strategy: FIFO Output queue 0/50, 0 drop, 0 dequeued !--- Queue size.

-

Las colas PVC también admiten CBWFQ y LLQ, que puede configurar mediante una política de servicio y los comandos del MQC. El siguiente ejemplo de resultado se capturó en el PVC de Frame Relay después de aplicarse una política de servicio de Calidad de servicio (QoS).

Router(config)# class-map gold Router(config-cmap)# match ip dscp 46 Router(config-cmap)# class-map silver Router(config-cmap)# match ip dscp 26 Router(config-cmap)# policy-map sample Router(config-pmap)# class gold Router(config-pmap-c)# priority 64 Router(config-pmap-c)# class silver Router(config-pmap-c)# bandwidth 32 Router(config)# map-class frame-relay map1 Router(config-map-class)# service-policy output sample Router(config-if)# frame-relay interface-dlci 20 Router(config-fr-dlci)# class map1 Router# show frame-relay PVC 20 PVC Statistics for interface Serial6/0:0 (Frame Relay DTE) DLCI = 20, DLCI USAGE = LOCAL, PVC STATUS = DELETED, INTERFACE = Serial6/0:0.1 input pkts 0 output pkts 0 in bytes 0 out bytes 0 dropped pkts 0 in FECN pkts 0 in BECN pkts 0 out FECN pkts 0 out BECN pkts 0 in DE pkts 0 out DE pkts 0 out bcast pkts 0 out bcast bytes 0 PVC create time 00:12:50, last time PVC status changed 00:12:37 cir 56000 bc 7000 be 0 byte limit 875 interval 125 mincir 28000 byte increment 875 Adaptive Shaping none pkts 0 bytes 0 pkts delayed 0 bytes delayed 0 shaping inactive traffic shaping drops 0 service policy sample Service-policy output: sample Class-map: gold (match-all) 0 packets, 0 bytes 5 minute offered rate 0 bps, drop rate 0 BPS Match: ip dscp 46 Weighted Fair Queueing Strict Priority Output Queue: Conversation 24 Bandwidth 64 (kbps) Burst 1600 (Bytes) (pkts matched/bytes matched) 0/0 (total drops/bytes drops) 0/0 Class-map: silver (match-all) 0 packets, 0 bytes 5 minute offered rate 0 BPS, drop rate 0 BPS Match: ip dscp 26 Weighted Fair Queueing Output Queue: Conversation 25 Bandwidth 32 (kbps) Max Threshold 64 (packets) !--- Queue information. (pkts matched/bytes matched) (depth/total drops/no-buffer drops) 0/0/0 Class-map: class-default (match-any) 0 packets, 0 bytes 5 minute offered rate 0 BPS, drop rate 0 BPS Match: any Output queue size 0/max total 600/drops 0 !--- Queue size.

Originalmente, el comando frame-relay holdq <size> map-class se utilizaba para configurar el tamaño de las colas de modelado de tráfico FIFO solamente. El tamaño máximo fue 512. En Cisco IOS Software Release 12.2, y a partir de IOS Software Release 12.2(4) este comando también afecta los búfers máximos en las colas de modelado de tráfico CBWFQ, según lo habilitado por el comando service-policy output map-class. El tamaño máximo es ahora 1024. Los valores predeterminados, que permanecen inalterados, son 40 para FIFO y 600 para CBWFQ.

Almacenamiento en cola a nivel de interfaz

Después de que las tramas de Frame Relay se ponen en cola en una cola PVC, se quitan de la cola a las colas de nivel de interfaz. El tráfico de todos los VC pasa a través de las colas de nivel de interfaz.

Dependiendo de las funciones configuradas, la cola de nivel de interfaz de Frame Relay utiliza uno de los siguientes mecanismos.

| Función | Mecanismo de cola predeterminado |

|---|---|

| FRTS | FIFO |

| FRF.12 | FIFO Dual |

| PIPQ | PIPQ |

Nota: PIPQ (cola de prioridad de interfaz PVC) anula FIFO y FIFO dual. En otras palabras, si habilita FRF.12, la estrategia de colocación en cola de la interfaz permanece como PIPQ.

Colas primero en entrar, primero en salir

Los pasos que se describe a continuación indican cómo la configuración de FRTS modifica el mecanismo aplicado para formar la cola hacia FIFO.

-

Cree una interfaz canalizada mediante el comando channel-group.

Router(config)# controller t1 6/0 Router(config-controller)# channel-group 0 ? timeslots List of timeslots in the channel group Router(config-controller)# channel-group 0 timeslots ? <1-24> List of timeslots which comprise the channel Router(config-controller)# channel-group 0 timeslots 12

-

Ejecute el comando show interface serial 6/0:0 y confirme que la interfaz T1 está utilizando la "estrategia de cola: equilibrada ponderada" predeterminada. En primer lugar, un paquete se envía a una cola elaborada en el nivel de VC. Luego se envía a la cola de la interfaz. En este caso, se aplicaría WFQ.

Router# show interface serial 6/0:0 Serial6/0:0 is up, line protocol is up (looped) Hardware is Multichannel T1 MTU 1500 bytes, BW 64 Kbit, DLY 20000 usec, reliability 253/255, txload 1/255, rxload 1/255 Encapsulation HDLC, crc 16, Data non-inverted Keepalive set (10 sec) Last input 00:00:08, output 00:00:08, output hang never Last clearing of "show interface" counters never Input queue: 0/75/0/0 (size/max/drops/flushes); Total output drops: Queueing strategy: weighted fair !--- Queue mechanism. Output queue: 0/1000/64/0 (size/max total/threshold/drops) !--- Queue size. Conversations 0/1/16 (active/max active/max total) !--- Queue information. Reserved Conversations 0/0 (allocated/max allocated) !--- Queue information. Available Bandwidth 48 kilobits/sec !--- Queue information. 5 minute input rate 0 bits/sec, 0 packets/sec 5 minute output rate 0 bits/sec, 0 packets/sec 5 packets input, 924 bytes, 0 no buffer Received 0 broadcasts, 14 runts, 0 giants, 0 throttles 14 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored, 0 abort 17 packets output, 2278 bytes, 0 underruns 0 output errors, 0 collisions, 0 interface resets 0 output buffer failures, 0 output buffers swapped out 0 carrier transitions no alarm present Timeslot(s) Used:12, subrate: 64Kb/s, transmit delay is 0 flags !--- Queue information. -

Cuando la estrategia de colocación en cola es WFQ, puede utilizar los comandos show queueing y show queue para confirmar.

Router# show queueing interface serial 6/0:0 Interface Serial6/0:0 queueing strategy: fair Input queue: 0/75/0/0 (size/max/drops/flushes); Total output drops: 0 Queueing strategy: weighted fair Output queue: 0/1000/64/0 (size/max total/threshold/drops) Conversations 0/1/16 (active/max active/max total) Reserved Conversations 0/0 (allocated/max allocated) Available Bandwidth 48 kilobits/sec Router# show queue serial 6/0:0 Input queue: 0/75/0/0 (size/max/drops/flushes); Total output drops: 0 Queueing strategy: weighted fair Output queue: 0/1000/64/0 (size/max total/threshold/drops) Conversations 0/1/16 (active/max active/max total) Reserved Conversations 0/0 (allocated/max allocated) Available Bandwidth 48 kilobits/sec -

Aplique FRTS usando el comando frame-relay traffic-shaping en el modo de configuración de la interfaz.

Router(config)# interface serial 6/0:0 Router(config-if)# frame-relay traffic-shaping

-

La aplicación de FRTS hace que el router cambie la estrategia de colocación en cola en las colas de nivel de interfaz a FIFO.

Router# show interface serial 6/0:0 Serial6/0:0 is up, line protocol is down (looped) Hardware is Multichannel T1 MTU 1500 bytes, BW 64 Kbit, DLY 20000 usec, reliability 255/255, txload 1/255, rxload 1/255 Encapsulation FRAME-RELAY, crc 16, Data non-inverted Keepalive set (10 sec) LMI enq sent 13, LMI stat recvd 0, LMI upd recvd 0, DTE LMI down LMI enq recvd 19, LMI stat sent 0, LMI upd sent 0 LMI DLCI 1023 LMI type is CISCO frame relay DTE Broadcast queue 0/64, broadcasts sent/dropped 0/0, interface broadcasts 0 Last input 00:00:06, output 00:00:06, output hang never Last clearing of "show interface" counters 00:02:16 Queueing strategy: FIFO !--- queue mechanism Output queue 0/40, 0 drops; input queue 0/75, 0 drops 5 minute input rate 0 bits/sec, 0 packets/sec 5 minute output rate 0 bits/sec, 0 packets/sec 19 packets input, 249 bytes, 0 no buffer Received 0 broadcasts, 0 runts, 0 giants, 0 throttles 0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored, 0 abort 19 packets output, 249 bytes, 0 underruns 0 output errors, 0 collisions, 0 interface resets 0 output buffer failures, 0 output buffers swapped out 0 carrier transitions no alarm present Timeslot(s) Used:12, subrate: 64Kb/s, transmit delay is 0 flags -

Dado que la estrategia de colocación en cola ahora es FIFO, cambia la salida de los comandos show queue y show queueing.

Router# show queueing interface serial 6/0:0 Interface Serial6/0:0 queueing strategy: none Router# Router# show queue serial 6/0:0 'Show queue' not supported with FIFO queueing.

La versión 12.2(4)T del software del IOS de Cisco introduce la función Modelado adaptable del tráfico de Frame Relay para la congestión de la interfaz, que está diseñada para minimizar los efectos de la demora y las caídas de paquetes causadas por la congestión de la interfaz. La función de Modelado adaptable de tráfico Frame Relay en la congestión de interfaz, ayuda a garantizar que el rechazo de paquetes ocurra en las colas del VC.

Al habilitar esta nueva función, el mecanismo de modelado de tráfico monitorea la congestión en la interfaz. Cuando el nivel de congestión excede un valor configurado denominado profundidad de cola, la velocidad de envío de todos los PVC se reduce a la velocidad mínima de información comprometida (minCIR). Tan pronto como la congestión de la interfaz cae por debajo de la profundidad de la cola, el mecanismo de modelado de tráfico cambia la velocidad de envío de los PVC a la velocidad de información comprometida (CIR). Este proceso garantiza el minCIR para los PVC cuando hay congestión de interfaz.

FIFO Dual

La cola de retransmisión de tramas, que aparece en la salida del comando show interface serial como FIFO dual, utiliza dos niveles de prioridad. La cola de alta prioridad gestiona paquetes de voz y paquetes de control como la interfaz de administración local (LMI). La cola de prioridad baja administra paquetes fragmentados (paquete de datos o no voz).

El mecanismo de colocación en cola a nivel interfaz cambia automáticamente a FIFO dual cuando habilita una de las siguientes características:

-

Fragmentación FRF.12: se habilita con el comando frame-relay fragment en el modo de configuración map-class. Los paquetes de datos mayores que el tamaño de paquete especificado en el comando frame-relay fragment se ponen primero en cola en una subcola WFQ. A continuación, se quitan de la cola y se fragmentan. Después de la fragmentación, se transmite el primer segmento. Los segmentos restantes esperan el siguiente momento disponible de transmisión para ese VC tal como lo determina el algoritmo de modelado. En este punto, los paquetes de voz pequeños y los paquetes de datos fragmentados se entrelazan desde otros PVC.

-

Priorización del protocolo de transporte en tiempo real (RTP): en un principio, los paquetes de datos pequeños también se clasificaban como pertenecientes a la cola de alta prioridad simplemente por su tamaño. La versión 12.0(6)T del software del IOS de Cisco modificó este comportamiento mediante la función RTP Prioritization (VoIPoFR). Reserva la cola de alta prioridad sólo para paquetes de control de voz y LMI. VoIPoFR clasifica los paquetes VoIP coincidiendo en el rango de puertos RTP UDP definido en una clase de mapa de Frame Relay. Todo el tráfico RTP dentro de este rango de puertos se envía a una cola de prioridad para el VC. Además, los paquetes de voz entran en la cola de alta prioridad en el nivel de interfaz. Todos los demás paquetes ingresan a la cola sin prioridad en el nivel de interfaz.

Nota: Esta funcionalidad supone que FRF.12 está configurado.

Para ver el tamaño de las dos colas, utilice el comando show interface. Los pasos siguientes muestran las colas primero en entrar, primero en salir) y describe la manera de modificar las medidas de las colas.

-

Ejecute el comando show interface serial. La cola de alta prioridad utiliza un límite de cola que es el doble del tamaño del límite de la cola de baja prioridad.

Router# show interface serial 6/0:0 Serial6/0:0 is up, line protocol is down Hardware is Multichannel T1 MTU 1500 bytes, BW 64 Kbit, DLY 20000 usec, reliability 255/255, txload 1/255, rxload 1/255 Encapsulation FRAME-RELAY, crc 16, Data non-inverted Keepalive set (10 sec) LMI enq sent 236, LMI stat recvd 0, LMI upd recvd 0, DTE LMI down LMI enq recvd 353, LMI stat sent 0, LMI upd sent 0 LMI DLCI 1023 LMI type is CISCO frame relay DTE Broadcast queue 0/64, broadcasts sent/dropped 0/0, interface broadcasts 0 Last input 00:00:02, output 00:00:02, output hang never Last clearing of "show interface" counters 00:39:22 Queueing strategy: dual FIFO! --- Queue mechanism. Output queue: high size/max/dropped 0/256/0 !--- High-priority queue. Output queue 0/128, 0 drops; input queue 0/75, 0 drops !--- Low-priority queue. 5 minute input rate 0 bits/sec, 0 packets/sec 5 minute output rate 0 bits/sec, 0 packets/sec 353 packets input, 4628 bytes, 0 no buffer Received 0 broadcasts, 0 runts, 0 giants, 0 throttles 0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored, 0 abort 353 packets output, 4628 bytes, 0 underruns 0 output errors, 0 collisions, 0 interface resets 0 output buffer failures, 0 output buffers swapped out 0 carrier transitions no alarm present Timeslot(s) Used:12, subrate: 64Kb/s, transmit delay is 0 flags -

Use el comando hold-queue {value} out para cambiar las medidas de la cola de interfaz.

Router(config)# interface serial 6/0:0 Router(config-if)# hold-queue ? <0-4096> Queue length Router(config-if)# hold-queue 30 ? in Input queue out Output queue Router(config-if)# hold-queue 30 out

-

Ejecute el comando show interface serial nuevamente y observe cómo los valores máximos de la "cola de salida" han cambiado.

Router# show interface serial 6/0:0 Serial6/0:0 is up, line protocol is up Hardware is Multichannel T1 MTU 1500 bytes, BW 64 Kbit, DLY 20000 usec, reliability 255/255, txload 1/255, rxload 1/255 Encapsulation FRAME-RELAY, crc 16, Data non-inverted Keepalive set (10 sec) LMI enq sent 249, LMI stat recvd 0, LMI upd recvd 0, DTE LMI down LMI enq recvd 372, LMI stat sent 0, LMI upd sent 0 LMI DLCI 1023 LMI type is CISCO frame relay DTE Broadcast queue 0/64, broadcasts sent/dropped 0/0, interface broadcasts 0 Last input 00:00:02, output 00:00:02, output hang never Last clearing of "show interface" counters 00:41:32 Queueing strategy: dual FIFO !--- Queue mechanism. Output queue: high size/max/dropped 0/60/0 !--- High-priority queue. Output queue 0/30, 0 drops; input queue 0/75, 0 drops !--- Low-priority queue. 5 minute input rate 0 bits/sec, 0 packets/sec 5 minute output rate 0 bits/sec, 0 packets/sec 372 packets input, 4877 bytes, 0 no buffer Received 0 broadcasts, 0 runts, 0 giants, 0 throttles 0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored, 0 abort 372 packets output, 4877 bytes, 0 underruns 0 output errors, 0 collisions, 0 interface resets 0 output buffer failures, 0 output buffers swapped out 0 carrier transitions no alarm present Timeslot(s) Used:12, subrate: 64Kb/s, transmit delay is 0 flags

PIPQ

Frame-Relay PIPQ está diseñado para configuraciones en las que VC separados transportan un único tipo de tráfico, como voz o datos. Esto permite asignar un valor de prioridad a cada PVC. PIPQ minimiza el retraso de cola o serialización en el nivel de la interfaz asegurándose de que se le preste servicio primero al VC de prioridad alta. PIPQ clasifica paquetes al extraer DLCI y buscar la prioridad en la estructura PVC que corresponda. El mecanismo PIPQ no examina el contenido del paquete. Por lo tanto, no toma decisiones según en los contenidos del paquete.

Utilice los siguientes comandos para configurar PIPQ.

-

Habilite PIPQ con el comando frame-relay interface-queue priority en la interfaz principal.

Router(config)# interface serial 6/0:0 Router(config-if)# frame-relay interface-queue priority Router(config-if)# end

-

Utilice el comando show interface serial para confirmar la "Estrategia de cola: prioridad DLCI". Este comando también muestra el tamaño actual y el número de caídas para cada cola.

Router# show interface serial 6/0:0 Serial6/0:0 is up, line protocol is up Hardware is Multichannel T1 MTU 1500 bytes, BW 64 Kbit, DLY 20000 usec, reliability 255/255, txload 1/255, rxload 1/255 Encapsulation FRAME-RELAY, crc 16, Data non-inverted Keepalive set (10 sec) LMI enq sent 119, LMI stat recvd 0, LMI upd recvd 0, DTE LMI down LMI enq recvd 179, LMI stat sent 0, LMI upd sent 0 LMI DLCI 1023 LMI type is CISCO frame relay DTE Broadcast queue 0/64, broadcasts sent/dropped 0/0, interface broadcasts 0 Last input 00:00:06, output 00:00:06, output hang never Last clearing of "show interface" counters 00:19:56 Input queue: 0/75/0/0 (size/max/drops/flushes); Total output drops: 0 Queueing strategy: DLCI priority !--- Queue mechanism. Output queue (queue priority: size/max/drops): high: 0/20/0, medium: 0/40/0, normal: 0/60/0, low: 0/80/0 !--- Queue size. 5 minute input rate 0 bits/sec, 0 packets/sec 5 minute output rate 0 bits/sec, 0 packets/sec 179 packets input, 2347 bytes, 0 no buffer Received 0 broadcasts, 0 runts, 0 giants, 0 throttles 0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored, 0 abort 179 packets output, 2347 bytes, 0 underruns 0 output errors, 0 collisions, 0 interface resets 0 output buffer failures, 0 output buffers swapped out 0 carrier transitions no alarm present Timeslot(s) Used:12, subrate: 64Kb/s, transmit delay is 0 flags -

Cree una clase de mapa de Frame Relay y asigne un nivel de prioridad a un VC usando el comando frame-relay interface-queue priority {high|medium|normal|low} . La prioridad PVC (Permanent Virtual Circuit/ Connection, Conexión/ Circuito Virtual Permanente) por defecto es normal. Todos los PVC con la misma prioridad comparten la misma cola de prioridad FIFO. Aplique la clase de mapa al VC. En el siguiente ejemplo de resultado, se asigna un PVC con el número DLCI 21 a la cola de interfaz de alta prioridad.

Router(config)# map-class frame-relay high_priority_class Router(config-map-class)# frame-relay interface-queue priority high Router(config-map-class)# exit Router(config)# interface serial 6/0:0.2 point Router(config-subif)# frame-relay interface-dlci 21 Router(config-fr-dlci)# class ? WORD map class name Router(config-fr-dlci)# class high_priority_class

-

Use los comandos show frame-relay PVC [dlci] y show queueing interface para confirmar el cambio de configuración.

Router# show frame PVC 21 PVC Statistics for interface Serial6/0:0 (Frame Relay DTE) DLCI = 21, DLCI USAGE = LOCAL, PVC STATUS = INACTIVE, INTERFACE = Serial6/0:0.2 input pkts 0 output pkts 0 in bytes 0 out bytes 0 dropped pkts 0 in FECN pkts 0 in BECN pkts 0 out FECN pkts 0 out BECN pkts 0 in DE pkts 0 out DE pkts 0 out bcast pkts 0 out bcast bytes 0 PVC create time 00:00:17, last time PVC status changed 00:00:17 cir 56000 BC 7000 be 0 byte limit 875 interval 125 mincir 28000 byte increment 875 Adaptive Shaping none pkts 0 bytes 0 pkts delayed 0 bytes delayed 0 shaping inactive traffic shaping drops 0 Queueing strategy: FIFO Output queue 0/40, 0 drop, 0 dequeued !--- Size of the PVC queue. priority high !--- All frames from this PVC are dequeued to the high-priority queue !--- at the interface. Router# show queueing interface serial 6/0:0 Interface Serial6/0:0 queueing strategy: priority Output queue utilization (queue/count) high/13 medium/0 normal/162 low/0 -

De modo opcional, configure el tamaño de cola de cada interfaz mediante el siguiente comando. Los tamaños predeterminados de las colas prioritarias de alta, media, normal y baja son paquetes de 20, 40, 60 y 80 respectivamente. Para configurar un valor diferente, utilice el comando frame-relay interface-queue priority [<high limit><medium limit><normal limit><low limit>] en el modo de configuración de la interfaz.

Una vez habilitada, PIPQ reemplaza cualquier otro mecanismo de colocación en cola de la interfaz Frame Relay, incluido FIFO dual. Si posteriormente habilita FRF.12 o FRTS, el mecanismo de colocación en cola a nivel de interfaz no volverá a FIFO dual. Además, PIPQ no se puede habilitar si ya se ha configurado un mecanismo de colocación en cola de fantasía no predeterminado en la interfaz. Se puede habilitar en presencia de WFQ si WFQ es el método predeterminado de colocación en cola de la interfaz. Al eliminar la configuración de PIPQ, la colocación en cola en el nivel de interfaz cambia al valor predeterminado o a FIFO dual, si FRF.12 está habilitado.

PIPQ aplica un almacenamiento en cola con prioridad estricta. Si el tráfico se quita continuamente de la cola a la cola de alta prioridad, el programador de colocación en cola programará la cola de alta prioridad y puede eliminar de manera efectiva las colas de menor prioridad. Por lo tanto, asegúrese de asignar PVC a la cola de prioridad alta.

Ajuste del anillo TX

El anillo TX es el búfer FIFO no priorizado empleado para almacenar tramas antes de la transmisión. Las interfaces Frame Relay utilizan un único anillo TX que comparten todos los VC. De forma predeterminada, el tamaño del anillo TX es de 64 paquetes para interfaces WAN seriales de mayor velocidad, incluyendo PA-T3+, PA-MC-2T3+ y PA-H. Los adaptadores de puerto WAN de menor velocidad ahora ajustan automáticamente el anillo TX a un valor de 2 paquetes. En otras palabras, los controladores de la interfaz establecen valores de anillo TX predeterminados exclusivos basados en la cantidad de ancho de banda.

| Cola | Ubicación | Métodos de almacenamiento en cola | Asignación de políticas de servicio | Comando a ajustar |

|---|---|---|---|---|

| Cola de hardware o anillo de transmisión por interfaz | Adaptador de puerto o módulo de red | sólo FIFO | No | tx-ring-limit |

| Cola de capa 3 por VC | Sistema de procesamiento de capa 3 o memorias intermedias de interfaz | FIFO, WFQ, CBWFQ o LLQ | Yes | Varía con el método para colocación en cola:

|

Nota: A diferencia de las interfaces ATM como PA-A3, las interfaces Frame Relay utilizan un único anillo de transmisión para la interfaz. No construyen un anillo separado para cada VC.

Es importante saber que el anillo TX es FIFO y no puede soportar un mecanismo de colocación en cola alternativo. De esta manera, al ajustar el anillo TX a un valor de 2 en interfaces de baja velocidad, se mueve la mayor parte del almacenamiento en memoria intermedia de paquetes a la cola de PVC donde los mecanismos de colocación en cola elaborada y las políticas de servicio de QoS sí se aplican.

La tabla siguiente enumera los adaptadores de puerto serial de la serie 7x00 para el ajuste descendente automático del anillo de transmisión.

| Número de pieza del adaptador de puerto | Ajuste automático de límite de timbre TX |

|---|---|

| Adaptadores de puerto serie de alta velocidad | |

| PA-H y PA-2H | Yes |

| PA-E3 y PA-T3 | Yes |

| PA-T3+ | Yes |

| Adaptadores de puerto serie multicanal | |

| PA-MC-2T3+ | Yes |

| PA-MC-2T1(=), PA-MC-4T1(=), PA-MC-8T1(=), PA-MC-8DSX1(=) | Yes |

| PA-MC-2E1/120(=), PA-MC-8E1/120(=) | Yes |

| PA-MC-T3 y PA-MC-E3 | Yes |

| PA-MC-8TE1+ | Yes |

| PA-STM1 | Yes |

| Adaptadores de puerto serial | |

| PA-4T, PA-4T+ | Yes |

| PA-4E1G | Yes |

| PA-8T-V35, PA-8T-X21, PA-8T-232 | Yes |

El tamaño del anillo de transmisión se reduce automáticamente cuando se habilita una función de optimización de voz. Además, la aplicación de PIPQ hace que el anillo de transmisión se apague automáticamente.

El siguiente resultado fue capturado en un router de la serie 7200 que ejecuta la versión 12.2(6) del software del IOS de Cisco.

7200-16# show controller serial 6/0:0

Interface Serial6/0:0

f/w rev 1.2.3, h/w rev 163, PMC freedm rev 1 idb = 0x6382B984

ds = 0x62F87C18, plx_devbase=0x3F020000, pmc_devbase=0x3F000000

Enabled=TRUE, DSX1 linestate=0x0,

Ds>tx_limited:1 Ds>tx_count:0 Ds>max_tx_count:20

alarm present

Timeslot(s) Used:1-24, subrate: 64Kb/s, transmit delay is 0 flags

Download delay = 0, Report delay = 0

IDB type=0xC, status=0x84208080

Pci shared memory = 0x4B16B200

Plx mailbox addr = 0x3F020040

RxFree queue=0x4B2FA280, shadow=0x62F9FA70

Rx freeq_wt=256, freeq_rd=256, ready_wt=1, ready_rd=0

TxFree queue=0x4B2FAAC0, shadow=0x62F8FA44

TX freeq_wt=4099, freeq_rd=4099, ready_wt=4, ready_rd=3

# of TxFree queue=4095

Freedm FIFO (0x6292BF64), hp=0x6292C034 indx=26, tp=0x6292CF5C indx=511

reset_count=0 resurrect_count=0

TX enqueued=0, throttled=0, unthrottled=0, started=10

tx_limited=TRUE tx_queue_limit=2

!--- Note "tx_limited=TRUE" when PIPQ is enabled. The "tx_queue_limit" value

!--- describes the value of the transmit ring.

7200-16(config)# interface serial 6/0:0

7200-16(config-if)# no frame-relay interface-queue priority

7200-16(config-if)# end

7200-16# show controller serial 6/0:0

Interface Serial6/0:0

f/w rev 1.2.3, h/w rev 163, PMC freedm rev 1 idb = 0x6382B984

Ds = 0x62F87C18, plx_devbase=0x3F020000, pmc_devbase=0x3F000000

Enabled=TRUE, DSX1 linestate=0x0,

Ds>tx_limited:0 Ds>tx_count:0 Ds>max_tx_count:20

alarm present

Timeslot(s) Used:1-24, subrate: 64Kb/s, transmit delay is 0 flags

Download delay = 0, Report delay = 0

IDB type=0xC, status=0x84208080

Pci shared memory = 0x4B16B200

Plx mailbox addr = 0x3F020040

RxFree queue=0x4B2FA280, shadow=0x62F9FA70

Rx freeq_wt=256, freeq_rd=256, ready_wt=1, ready_rd=0

TxFree queue=0x4B2FAAC0, shadow=0x62F8FA44

TX freeq_wt=4099, freeq_rd=4099, ready_wt=4, ready_rd=3

# of TxFree queue=4095

Freedm FIFO (0x6292BF64), hp=0x6292C034 indx=26, tp=0x6292CF5C indx=511

reset_count=0 resurrect_count=0

TX enqueued=0, throttled=0, unthrottled=0, started=11

tx_limited=FALSE

!--- Transmit ring value has changed.

Información Relacionada

- Configuración de CBWFQ en PVC de Frame Relay

- Cola de tiempo de latencia bajo para Frame Relay

- Frame Relay PVC Interface Priority Queueing

- Configuración del modelado del tráfico de retransmisión de tramas en routers 7200 y plataformas inferiores

- Modelado del Tráfico de Frame Relay con QoS distribuido en las series Cisco 7500

- ‘Configuración del paquete de marcación en PVC de Frame Relay’

- Cola de tiempo de latencia bajo para Frame Relay

- Páginas de soporte de Frame_Relay

- Páginas de soporte de Qos (calidad de servicio)

- Soporte Técnico - Cisco Systems

Contacte a Cisco

- Abrir un caso de soporte

- (Requiere un Cisco Service Contract)

Comentarios

Comentarios