Solucionar problemas de "QM_SANITY_WARNING" mensaje en el router serie 12000

Opciones de descarga

-

ePub (172.5 KB)

Visualice en diferentes aplicaciones en iPhone, iPad, Android, Sony Reader o Windows Phone -

Mobi (Kindle) (178.2 KB)

Visualice en dispositivo Kindle o aplicación Kindle en múltiples dispositivos

Lenguaje no discriminatorio

El conjunto de documentos para este producto aspira al uso de un lenguaje no discriminatorio. A los fines de esta documentación, "no discriminatorio" se refiere al lenguaje que no implica discriminación por motivos de edad, discapacidad, género, identidad de raza, identidad étnica, orientación sexual, nivel socioeconómico e interseccionalidad. Puede haber excepciones en la documentación debido al lenguaje que se encuentra ya en las interfaces de usuario del software del producto, el lenguaje utilizado en función de la documentación de la RFP o el lenguaje utilizado por un producto de terceros al que se hace referencia. Obtenga más información sobre cómo Cisco utiliza el lenguaje inclusivo.

Acerca de esta traducción

Cisco ha traducido este documento combinando la traducción automática y los recursos humanos a fin de ofrecer a nuestros usuarios en todo el mundo contenido en su propio idioma. Tenga en cuenta que incluso la mejor traducción automática podría no ser tan precisa como la proporcionada por un traductor profesional. Cisco Systems, Inc. no asume ninguna responsabilidad por la precisión de estas traducciones y recomienda remitirse siempre al documento original escrito en inglés (insertar vínculo URL).

Introducción

Este documento describe el procedimiento para depurar los mensajes de agotamiento del buffer de paquetes que pueden ocurrir en diferentes tarjetas de línea en un router de Cisco de la serie 12000 que ejecuta IOS. Es demasiado común ver que se desperdician valiosos recursos y tiempo en reemplazar el hardware que realmente funciona correctamente debido a la falta de conocimiento sobre la administración del búfer GSR.

Prerequisites

Requirements

El lector debe tener una descripción general de la arquitectura del router de la serie 12000 de Cisco.

Componentes Utilizados

La información que contiene este documento se basa en las siguientes versiones de software y hardware.

- ’Router de Internet la serie Cisco 12000’

- Versión del software Cisco IOS® que admite el router de switch Gigabit

La información que contiene este documento se creó a partir de los dispositivos en un ambiente de laboratorio específico. Todos los dispositivos utilizados en este documento se inician con una configuración desactivada (predeterminada). If your network is live, make sure that you understand the potential impact of any command.

Convenciones

Problema

Los routers de Cisco serie GSR o 12000 cuentan con una arquitectura verdaderamente distribuida. Esto significa que cada LC ejecuta su propia copia de la imagen del software del IOS de Cisco y tiene la inteligencia necesaria para completar la decisión de reenvío de paquetes por sí misma. Cada tarjeta de línea tiene su propia

- Búsqueda de reenvío

- Gestión de búfer de paquetes

- QOS

- Control de flujo

Una de las operaciones más importantes durante el switching de paquetes en GSR es la administración del búfer, que se realiza mediante varios ASIC de administración de búfer (BMA) ubicados en las tarjetas de línea. A continuación se muestran algunos mensajes relacionados con la administración del búfer GSR que podrían aparecer en los registros del router mientras está en producción. En la siguiente sección discutiremos los diferentes disparadores que podrían causar que estos mensajes aparezcan en los registros del router y cuáles son las acciones correctivas que se deben realizar para mitigar el problema. En algunas situaciones, esto también podría llevar a la pérdida de paquetes, que podría manifestarse como inestabilidad de protocolo y causar impacto en la red.

%EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted

SLOT 1:Sep 16 19:06:40.003 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(1) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:45.943 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(0) are available in ToFab FreeQ pool# 1

SLOT 0:Sep 16 19:06:46.267 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(2) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:47.455 UTC: %EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted. Recarving the ToFab buffers

SLOT 8:Sep 16 19:06:47.471 UTC: %EE192-3-BM_QUIESCE:

Solución

Background

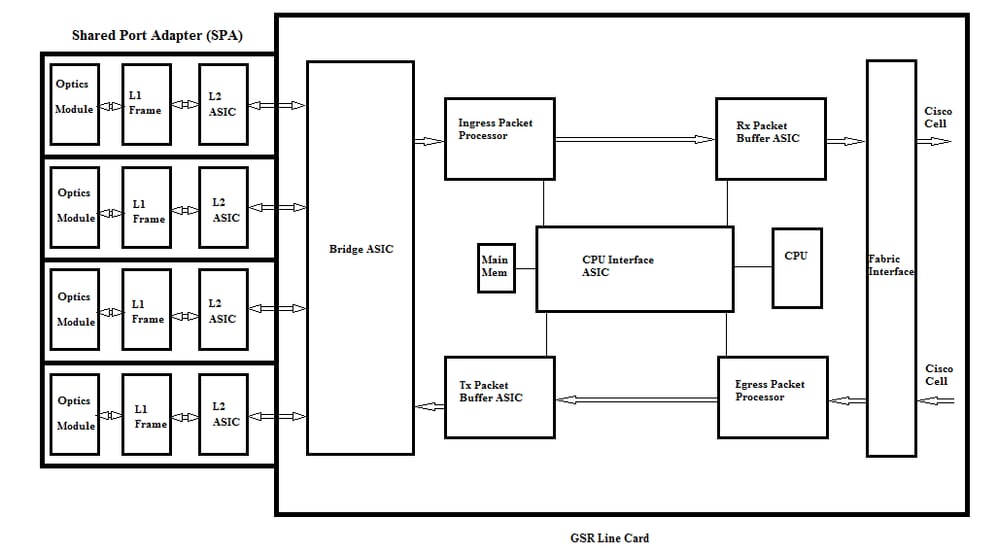

Para solucionar los errores de advertencia QM-SANITY, necesitamos entender el flujo de paquetes en una tarjeta de línea GSR. La siguiente figura explica los bloques principales de una tarjeta de línea C12k y la trayectoria de flujo de paquetes.

La tarjeta de línea (LC) en un router de Internet de la serie 12000 de Cisco tiene dos tipos de memoria:

- Memoria del procesador o de la ruta (RAM dinámica - DRAM): Esta memoria permite principalmente al procesador incorporado ejecutar el software del IOS de Cisco y almacenar tablas de ruteo de red (Base de información de reenvío - FIB, adyacencia)

- Memoria de paquetes (RAM dinámica sincrónica - SDRAM): La memoria de paquetes de tarjeta de línea almacena temporalmente los paquetes de datos a la espera de decisiones de conmutación por parte del procesador de tarjeta de línea.

Como se observa en la imagen anterior, la tarjeta de línea GSR tiene un ASIC de búfer de paquetes especializado (circuito integrado específico de la aplicación), uno en cada dirección del flujo de tráfico que proporciona acceso a la memoria del paquete. Estos ASIC también conocidos como ASIC de administración de búfer ( BMA) realizan la función de almacenamiento en búfer de paquetes y administración de cola de búfer en la tarjeta de línea. Para admitir altas velocidades de rendimiento/reenvío, la memoria de paquetes en cualquier dirección se divide en grupos de memoria de diferentes tamaños diseñados para reenviar paquetes de diversos tamaños de MTU.

Las tramas recibidas por las tarjetas del módulo de interfaz de capa física (PLIM) se procesan en la capa 2 y se DMAed a una memoria local en la tarjeta PLIM. Una vez completada la unidad de datos recibidos, un ASIC en el PLIM se pone en contacto con el BMA de entrada y solicita un búfer del tamaño adecuado. Si se concede el búfer, el paquete se traslada a la memoria del paquete de ingreso de la tarjeta de línea. Si no hay búferes disponibles, el paquete se descarta y el contador de interfaz ignorada se activará. El procesador de paquetes de ingreso realiza el procesamiento de funciones en el paquete, toma la decisión de reenvío y mueve el paquete a la cola toFab correspondiente a la tarjeta de línea de egreso. La interfaz de fabric ASIC (FIA) segmenta el paquete en celdas de Cisco y la celda se transmite al fabric de switch. Luego, el FIA recibe los paquetes del entramado del switch en la tarjeta de línea de salida y pasa a las colas Frfab donde se reensamblan, luego al PLIM de salida y finalmente se envían en el cable.

La decisión del FrFab BMA de seleccionar el búfer de un conjunto de búferes concreto se basa en la decisión tomada por el motor de switching de tarjeta de línea de entrada. Dado que todas las colas en toda la caja son del mismo tamaño y en el mismo orden, el motor de conmutación le dice a la LC de transmisión que coloque el paquete en la cola del mismo número desde la cual ingresó al router.

Mientras se conmuta el paquete, el tamaño de la cola de un conjunto de búfer determinado en la tarjeta de línea de entrada que se utilizó para mover el paquete se reducirá en uno hasta que el BMA en la tarjeta de línea de salida devuelva el búfer. En este caso, también debemos tener en cuenta que la gestión completa del búfer la realiza el ASIC de gestión de búfer en el hardware y, para un funcionamiento sin fallos, es necesario que el BMA devuelva los búferes al conjunto original desde el que se originaron.

Existen tres escenarios donde la administración del buffer de paquetes GSR puede experimentar estrés o fallas que pueden conducir a la pérdida de paquetes. A continuación se muestran los tres escenarios.

Escenario 1:

La administración de la cola de hardware falla. Esto sucede cuando el BMA de salida no puede devolver el buffer de paquetes o devuelve el buffer de paquetes a un pool de buffer incorrecto. Si las memorias intermedias vuelven al conjunto incorrecto, veremos que algunos conjuntos de memoria intermedia crecen y algunos conjuntos de memoria intermedia se agotan durante un período de tiempo y, finalmente, afectan a los paquetes con el tamaño del conjunto de memoria intermedia que se agota. Empezaremos a ver las advertencias de integridad de QM a medida que el buffer de paquetes se agota y cruza el umbral de advertencia.

Utilice el comando QM sanity debugs y show controllers tofab queues para verificar si esta condición le afecta. Consulte la sección de resolución de problemas para obtener información sobre cómo activar los umbrales de integridad de QM.

Esta condición es causada generalmente por hardware defectuoso. Verifique las siguientes salidas en el router y busque errores de paridad o caídas de la tarjeta de línea. La solución sería reemplazar la tarjeta de línea.

show controllers fia

show context all

show log

Ejemplo:

Desde los debugs de cordura de QM y show controller tofab queue podemos ver que el Pool 2 está creciendo en tamaño mientras que el Pool 4 se está quedando sin recursos. Esto indica que el Grupo 4 está perdiendo memorias intermedias y está siendo devuelto al Grupo 2.

Depuraciones de cordura de QM:

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 1: Carve Size 102001: Current Size 73078

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 2: Carve Size 78462: Current Size 181569

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 3: Carve Size 57539: Current Size 6160

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 4: Carve Size 22870: Current Size 67

SLOT 5:Oct 25 04:41:03.286 UTC: IPC FreeQ: Carve Size 600: Current Size 600

show controllers tofab queues:

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 13542 13448 73078 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 131784 131833 181569 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 184620 182591 6160 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 239113 238805 67 262143

Escenario 2:

Congestión de tráfico en el dispositivo de salto siguiente o en la trayectoria de reenvío. En esta situación, el dispositivo al que el GSR alimenta el tráfico no puede procesar a la velocidad del GSR y, como resultado, el dispositivo de salto siguiente envía tramas de pausa hacia el GSR pidiéndole que reduzca la velocidad. Si el control de flujo está habilitado en las tarjetas PLIM GSR , el router respetará las tramas de pausa y comenzará a almacenar en búfer los paquetes. Finalmente, el router se quedará sin búfers, lo que causará los mensajes de error QM Sanity y las caídas de paquetes. Empezaremos a ver las advertencias de integridad de QM a medida que el buffer de paquetes se agota y cruza el umbral de advertencia. Consulte la sección de troubleshooting para obtener información sobre cómo encontrar los umbrales de integridad de QM.

Utilice el comando show interface output en la interfaz de egreso para verificar si el router se ve afectado por este escenario. La siguiente captura brinda un ejemplo de una interfaz que recibe tramas de pausa. El plan de acción consistirá en observar la causa de la congestión en el dispositivo de salto siguiente.

GigabitEthernet6/2 is up, line protocol is up

Small Factor Pluggable Optics okay

Hardware is GigMac 4 Port GigabitEthernet, address is 000b.455d.ee02 (bia 000b.455d.ee02)

Description: Cisco Sydney Lab

Internet address is 219.158.33.86/30

MTU 1500 bytes, BW 500000 Kbit, DLY 10 usec, rely 255/255, load 154/255

Encapsulation ARPA, loopback not set

Keepalive set (10 sec)

Full Duplex, 1000Mbps, link type is force-up, media type is LX

output flow-control is on, input flow-control is on

ARP type: ARPA, ARP Timeout 04:00:00

Last input 00:00:02, output 00:00:02, output hang never

Last clearing of "show interface" counters 7w1d

Queueing strategy: random early detection (WRED)

Output queue 0/40, 22713601 drops; input queue 0/75, 736369 drops

Available Bandwidth 224992 kilobits/sec

30 second input rate 309068000 bits/sec, 49414 packets/sec

30 second output rate 303400000 bits/sec, 73826 packets/sec

143009959974 packets input, 88976134206186 bytes, 0 no buffer

Received 7352 broadcasts, 0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored

0 watchdog, 7352 multicast, 45 pause input

234821393504 packets output, 119276570730993 bytes, 0 underruns

Transmitted 73201 broadcasts

0 output errors, 0 collisions, 0 interface resets

0 babbles, 0 late collision, 0 deferred

0 lost carrier, 0 no carrier, 0 pause output

0 output buffer failures, 0 output buffers swapped out

Escenario 3:

En momentos de sobresuscripción debido a un diseño de red deficiente/ráfagas de tráfico/ataques DOS. La advertencia de integridad de QM puede ocurrir si hay una condición de tráfico alto sostenido donde se dirige más tráfico al router que lo que las tarjetas de línea pueden manejar.

Para rootcause esto, verifique las velocidades de tráfico en todas las interfaces en el router. Esto revelará si alguno de los links de alta velocidad está congestionando links lentos.

Utilice el comando show interface output.

Comandos para Troubleshooting

Para comprobar el nivel de integridad de QM actual para una LC

-

Asociar a LC

-

Vaya al modo enable (activar)

-

Ejecute el comando test fab

-

Recopile la salida de "qm_sanity_info"

-

Opción q para salir de la línea de comandos test fab

-

Salir de LC

Para configurar los parámetros de integridad de QM

- cambiar al modo de configuración

- Ejecute hw-module slot <slot#> qm-sanity tofab warning freq <>

Para habilitar/deshabilitar los debugs de integridad de QM

- Asociar a LC

-

Vaya al modo enable (activar)

-

Ejecute el comando test fab

-

Ejecute "qm_sanity_debug". Ejecute de nuevo y detendrá las depuraciones

-

Opción q para salir de la línea de comandos test fab

-

Salir de LC

Para comprobar las estadísticas básicas de la interfaz de fabric GSR

- show controller fia

Para comprobar las colas Tofab

- show controllers tofab queues

Para comprobar las colas Frfab

- show controller frfab queues

Ejemplo:

El siguiente resultado se extrae de un router Lab en funcionamiento para demostrar los resultados de los comandos.

GSR-1-PE-5#show controller fia

Fabric configuration: 10Gbps bandwidth (2.4Gbps available), redundant fabric

Master Scheduler: Slot 17 Backup Scheduler: Slot 16

Fab epoch no 0 Halt count 0

From Fabric FIA Errors

-----------------------

redund overflow 0 cell drops 0

cell parity 0

Switch cards present 0x001F Slots 16 17 18 19 20

Switch cards monitored 0x001F Slots 16 17 18 19 20

Slot: 16 17 18 19 20

Name: csc0 csc1 sfc0 sfc1 sfc2

-------- -------- -------- -------- --------

los 0 0 0 0 0

state Off Off Off Off Off

crc16 0 0 0 0 0

To Fabric FIA Errors

-----------------------

sca not pres 0 req error 0 uni fifo overflow 0

grant parity 0 multi req 0 uni fifo undrflow 0

cntrl parity 0 uni req 0

multi fifo 0 empty dst req 0 handshake error 0

cell parity 0

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_debug

QM Sanity Debug enabled

BFLC (? for help) [qm_sanity_debug]:

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

QM Sanity Debug disabled

BFLC (? for help) [qm_sanity_debug]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 20 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exi

Disconnecting from slot 1.

Connection Duration: 00:01:09

GSR-1-PE-5#config t

Enter configuration commands, one per line. End with CNTL/Z.

GSR-1-PE-5(config)#hw-module slot 1 qm-sanity tofab warning freq 10

GSR-1-PE-5(config)#end

GSR-1-PE-5#attach 1

02:57:25: %SYS-5-CONFIG_I: Configured from console by console

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 10 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exit

Disconnecting from slot 1.

Connection Duration: 00:00:27

GSR-1-PE-5#execute-on all show controllers tofab queues

========= Line Card (Slot 0) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262141/262141 buffers specified/carved

265028848/265028848 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

107232/107232 (buffers specified/carved), 40.90%, 80 byte data size

601 107832 107232 262143

73232/73232 (buffers specified/carved), 27.93%, 608 byte data size

107833 181064 73232 262143

57539/57539 (buffers specified/carved), 21.94%, 1616 byte data size

181065 238603 57539 262143

23538/23538 (buffers specified/carved), 8.97%, 4592 byte data size

238604 262141 23538 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

155 154 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

15 2191(hpr) 0 0 0 0

Multicast 2048 0 0 0 262143

2049 0 0 0 262143

========= Line Card (Slot 1) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: 26000000, carve base: 26010000

268369920 bytes carve size, 4 SDRAM bank(s), 32768 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262140/261472 buffers specified/carved

267790176/264701344 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 601 102601 102001 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 102602 181063 78462 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 181064 238602 57539 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 238603 261472 22870 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

30 85 84 600 262143

Raw Queue (high priority):

27 0 0 0 65368

Raw Queue (medium priority):

28 0 0 0 32684

Raw Queue (low priority):

31 0 0 0 16342

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

=============================================================

::::::::::::::::::::

Hi Priority

0 2176(hpr) 0 0 0

1 2177(hpr) 0 0 0

2 2178(hpr) 0 0 0

3 2179(hpr) 0 0 0

4 2180(hpr) 553 552 0

5 2181(hpr) 0 0 0

6 2182(hpr) 0 0 0

7 2183(hpr) 0 0 0

8 2184(hpr) 0 0 0

9 2185(hpr) 0 0 0

10 2186(hpr) 0 0 0

11 2187(hpr) 0 0 0

12 2188(hpr) 0 0 0

13 2189(hpr) 0 0 0

14 2190(hpr) 0 0 0

15 2191(hpr) 0 0 0

Multicast

2048 0 0 0

2049 0 0 0

2050 0 0 0

2051 0 0 0

2052 0 0 0

2053 0 0 0

2054 0 0 0

2055 0 0 0

========= Line Card (Slot 3) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4112 bytes, min buffer data size 80 bytes

262142/262142 buffers specified/carved

230886224/230886224 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

3 non-IPC free queues:

94155/94155 (buffers specified/carved), 35.91%, 80 byte data size

601 94755 94155 262143

57539/57539 (buffers specified/carved), 21.94%, 608 byte data size

94756 152294 57539 262143

109848/109848 (buffers specified/carved), 41.90%, 1616 byte data size

152295 262142 109848 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

207 206 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

1 0 0 0 262143

2 0 0 0 262143

3 0 0 0 262143

:::::::::::::::::::::::::::

2049 0 0 0 262143

2050 0 0 0 262143

2051 0 0 0 262143

2052 0 0 0 262143

2053 0 0 0 262143

2054 0 0 0 262143

2055 0 0 0 262143

GSR-1-PE-5#execute-on slot 2 show controller frfab queues

========= Line Card (Slot 2) =========

Carve information for FrFab buffers

SDRAM size: 268435456 bytes, address: D0000000, carve base: D241D100

230567680 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

235926/235926 buffers specified/carved

226853664/226853664 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

96484/96484 (buffers specified/carved), 40.89%, 80 byte data size

11598 11597 96484 262143

77658/77658 (buffers specified/carved), 32.91%, 608 byte data size

103116 103115 77658 262143

40005/40005 (buffers specified/carved), 16.95%, 1616 byte data size

178588 178587 40005 262143

21179/21179 (buffers specified/carved), 8.97%, 4592 byte data size

214748 235926 21179 262143

IPC Queue:

600/600 (buffers specified/carved), 0.25%, 4112 byte data size

66 65 600 262143

Multicast Raw Queue:

0 0 0 58981

Multicast Replication Free Queue:

235930 262143 26214 262143

Raw Queue (high priority):

78 77 0 235927

Raw Queue (medium priority):

11596 11595 0 58981

Raw Queue (low priority):

0 0 0 23592

Interface Queues:

Interface Queue# Head Tail Length Threshold

pkts pkts

======================================================

0 0 103107 103106 0 32768

3 178588 178587 0 32768

1 4 103110 103109 0 32768

7 11586 11585 0 32768

2 8 0 0 0 32768

11 0 0 0 32768

3 12 0 0 0 32768

15 0 0 0 32768

GSR-1-PE-5#

Historial de revisiones

| Revisión | Fecha de publicación | Comentarios |

|---|---|---|

1.0 |

30-Jul-2017

|

Versión inicial |

Con la colaboración de ingenieros de Cisco

- Shabeer MansoorCisco TAC

Contacte a Cisco

- Abrir un caso de soporte

- (Requiere un Cisco Service Contract)

Comentarios

Comentarios