Dépannage du message " ; QM_SANITY_WARNING" ; sur le routeur de la gamme 12000

Options de téléchargement

-

ePub (172.3 KB)

Consulter à l’aide de différentes applications sur iPhone, iPad, Android ou Windows Phone -

Mobi (Kindle) (177.9 KB)

Consulter sur un appareil Kindle ou à l’aide d’une application Kindle sur plusieurs appareils

Langage exempt de préjugés

Dans le cadre de la documentation associée à ce produit, nous nous efforçons d’utiliser un langage exempt de préjugés. Dans cet ensemble de documents, le langage exempt de discrimination renvoie à une langue qui exclut la discrimination en fonction de l’âge, des handicaps, du genre, de l’appartenance raciale de l’identité ethnique, de l’orientation sexuelle, de la situation socio-économique et de l’intersectionnalité. Des exceptions peuvent s’appliquer dans les documents si le langage est codé en dur dans les interfaces utilisateurs du produit logiciel, si le langage utilisé est basé sur la documentation RFP ou si le langage utilisé provient d’un produit tiers référencé. Découvrez comment Cisco utilise le langage inclusif.

À propos de cette traduction

Cisco a traduit ce document en traduction automatisée vérifiée par une personne dans le cadre d’un service mondial permettant à nos utilisateurs d’obtenir le contenu d’assistance dans leur propre langue. Il convient cependant de noter que même la meilleure traduction automatisée ne sera pas aussi précise que celle fournie par un traducteur professionnel.

Introduction

Ce document décrit la procédure de débogage des messages d'épuisement de mémoire tampon de paquets qui peuvent se produire sur différentes cartes de ligne dans un routeur cisco de la gamme 12000 exécutant IOS. Il est bien trop fréquent de voir du temps précieux et des ressources gaspillées pour remplacer le matériel qui fonctionne réellement correctement en raison d'un manque de connaissances sur la gestion de la mémoire tampon GSR.

Conditions préalables

Exigences

Le lecteur doit avoir une vue d'ensemble de l'architecture des routeurs de la gamme Cisco 12000.

Composants utilisés

Les informations contenues dans ce document sont basées sur les versions de matériel et de logiciel suivantes :

- Routeur Internet de la gamme Cisco 12000

- Version du logiciel Cisco IOS® prenant en charge le routeur de commutation Gigabit

The information in this document was created from the devices in a specific lab environment. Tous les périphériques utilisés dans ce document sont démarrés avec une configuration effacée (par défaut). If your network is live, make sure that you understand the potential impact of any command.

Conventions

Pour plus d'informations sur les conventions utilisées dans ce document, reportez-vous à Conventions relatives aux conseils techniques Cisco.

Problème

Les routeurs Cisco de la gamme GSR ou 12000 possèdent une architecture véritablement distribuée. Cela signifie que chaque LC exécute sa propre copie de l'image du logiciel Cisco IOS et dispose de l'intelligence nécessaire pour prendre la décision de transférer les paquets. Chaque carte de ligne a sa propre fonction

- Recherche de transfert

- Gestion des tampons de paquets

- QOS

- Contrôle de flux

L'une des opérations les plus importantes lors de la commutation de paquets dans GSR est la gestion de tampon qui est effectuée par divers ASIC de gestion de tampon ( BMA) situés dans les cartes de ligne. Voici quelques messages relatifs à la gestion de la mémoire tampon GSR qui pourraient apparaître dans les journaux du routeur pendant la production. Dans la section suivante, nous aborderons les différents déclencheurs qui peuvent provoquer l’affichage de ces messages dans les journaux du routeur et les mesures correctives à prendre pour atténuer le problème. Dans certaines situations, cela peut également entraîner une perte de paquets qui peut se manifester par des failles de protocole et avoir un impact sur le réseau.

%EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted

SLOT 1:Sep 16 19:06:40.003 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(1) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:45.943 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(0) are available in ToFab FreeQ pool# 1

SLOT 0:Sep 16 19:06:46.267 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(2) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:47.455 UTC: %EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted. Recarving the ToFab buffers

SLOT 8:Sep 16 19:06:47.471 UTC: %EE192-3-BM_QUIESCE:

Solution

Fond

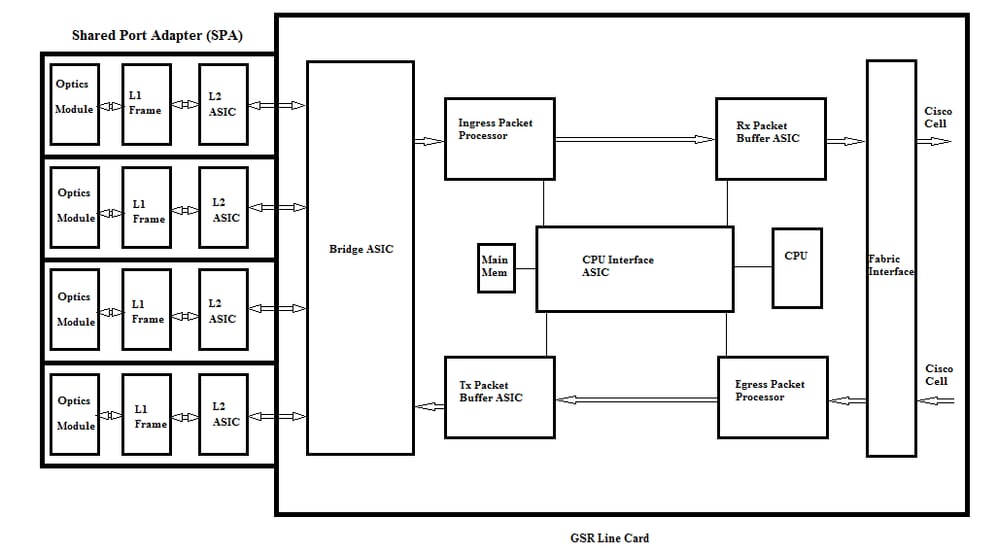

Pour dépanner les erreurs d'avertissement QM-SANITY, nous devons comprendre le flux de paquets sur une carte de ligne GSR. La figure ci-dessous décrit les principaux blocs d'une carte de ligne C12k et le chemin de flux de paquets.

La carte de ligne (LC) d'un routeur Internet de la gamme Cisco 12000 dispose de deux types de mémoire :

- Mémoire de routage ou de processeur (DRAM - Dynamic RAM) : cette mémoire permet principalement au processeur embarqué d'exécuter la plate-forme logicielle Cisco IOS et de stocker les tables de routage réseau (FIB, contiguïté)

- Mémoire de paquets (Synchronous Dynamic RAM - SDRAM) : la mémoire de paquets de la carte de ligne stocke temporairement les paquets de données en attente de décisions de commutation par le processeur de la carte de ligne.

Comme le montre l'image ci-dessus, la carte de ligne GSR a un circuit ASIC (Application Specific Integrated Circuit) de tampon de paquets spécialisé, un dans chaque sens de flux de trafic qui fournit l'accès à la mémoire de paquets. Ces circuits ASIC, également connus sous le nom d'ASIC de gestion de tampon ( BMA), assurent la fonction de mise en tampon de paquets et de gestion de file d'attente de tampon sur la carte de ligne. Pour prendre en charge des débits/débits de transfert élevés, la mémoire de paquets dans les deux directions est découpée en pools de mémoire de différentes tailles conçus pour transférer des paquets de différentes tailles de MTU.

Les trames reçues par les cartes PLIM (Physical Layer Interface Module) sont traitées au niveau de la couche 2 et envoyées par DMA à une mémoire locale de la carte PLIM. Une fois l'unité de données reçue terminée, un ASIC dans le PLIM contacte le BMA d'entrée et demande une mémoire tampon de taille appropriée. Si la mémoire tampon est allouée, le paquet se déplace vers la mémoire de paquets d'entrée de la carte de ligne. Si aucune mémoire tampon n’est disponible, le paquet est abandonné et le compteur d’interface ignoré s’active. Le processeur de paquets d'entrée effectue le traitement des fonctions sur le paquet, prend la décision de transfert et déplace le paquet vers la file d'attente toFab correspondant à la carte de ligne de sortie. L'ASIC (FIA) de l'interface de matrice segmente le paquet en cellules cisco et la cellule est transmise à la matrice de commutation. Les paquets sont ensuite reçus de la matrice de commutation par le FIA sur la carte de ligne de sortie et passent aux files d'attente Frfab où ils sont réassemblés, puis au PLIM de sortie, et enfin envoyés sur le câble.

La décision de la FrFab BMA de sélectionner le tampon dans un pool de tampons particulier est basée sur la décision prise par le moteur de commutation de carte de ligne d'entrée. Comme toutes les files d'attente de la boîte entière sont de la même taille et dans le même ordre, le moteur de commutation demande au LC émetteur de placer le paquet dans la même file d'attente de numéros à partir de laquelle il est entré dans le routeur.

Pendant la commutation du paquet, la taille de file d'attente d'un pool de tampons particulier au niveau de la carte de ligne d'entrée qui a été utilisée pour déplacer le paquet sera décrémentée de un jusqu'à ce que le BMA dans la carte de ligne de sortie renvoie le tampon. Ici, nous devons également noter que la gestion complète des tampons est effectuée dans le matériel par les ASIC de gestion des tampons et pour un fonctionnement sans faille, il est nécessaire que le BMA retourne les tampons au pool d'origine d'où ils proviennent.

Il existe trois scénarios dans lesquels la gestion de la mémoire tampon de paquets GSR peut subir une contrainte ou une défaillance entraînant une perte de paquets. Voici les trois scénarios.

Scénario 1 :

La gestion des files d'attente matérielles échoue. Cela se produit lorsque le BMA de sortie ne parvient pas à renvoyer le tampon de paquets ou renvoie le tampon de paquets vers un pool de tampons incorrect. Si les tampons sont renvoyés vers le pool incorrect, nous verrons certains pools de tampons augmenter et certains s'épuiser sur une certaine période de temps et finir par effectuer des paquets avec la taille du pool de tampons qui s'épuise. Nous commencerons à voir les avertissements QM-Sanity lorsque le tampon de paquets s'épuise et dépasse le seuil d'avertissement.

Utilisez les commandes QM sanity debugs et show controllers tofab queues pour vérifier si vous êtes affecté par cette condition. Reportez-vous à la section de dépannage pour savoir comment activer les seuils de validité de QM.

Cette condition est généralement due à un matériel défectueux. Vérifiez les sorties ci-dessous sur le routeur et recherchez les erreurs de parité ou les pannes de la carte de ligne. La solution consiste à remplacer la carte de ligne.

show controllers fia

show context all

show log

Exemple :

À partir des débogages de QM sanity et de la file d'attente show controller tofab, nous pouvons voir que la taille du pool 2 augmente alors que celle du pool 4 est faible. Cela indique que le pool 4 perd des mémoires tampons et qu'il est renvoyé au pool 2.

Débogages QM sanity :

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 1: Carve Size 102001: Current Size 73078

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 2: Carve Size 78462: Current Size 181569

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 3: Carve Size 57539: Current Size 6160

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 4: Carve Size 22870: Current Size 67

SLOT 5:Oct 25 04:41:03.286 UTC: IPC FreeQ: Carve Size 600: Current Size 600

show controllers tofab queues :

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 13542 13448 73078 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 131784 131833 181569 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 184620 182591 6160 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 239113 238805 67 262143

Scénario 2 :

Congestion du trafic sur le périphérique du tronçon suivant ou sur le chemin de transmission. Dans ce scénario, le périphérique auquel le GSR alimente le trafic ne peut pas traiter à la vitesse du GSR et, par conséquent, le périphérique du saut suivant envoie des trames de pause vers le GSR lui demandant de ralentir. Si le contrôle de flux est activé sur les cartes GSR PLIM , le routeur honorera les trames de pause et commencera à mettre les paquets en mémoire tampon. Le routeur finit par manquer de mémoires tampon, ce qui entraîne des messages d'erreur QM Sanity et des abandons de paquets. Nous commencerons à voir les avertissements QM-Sanity lorsque le tampon de paquets s'épuise et dépasse le seuil d'avertissement. Reportez-vous à la section de dépannage pour trouver les seuils de validité de QM.

Utilisez la sortie show interface sur l'interface de sortie pour vérifier si le routeur est affecté par ce scénario. La capture ci-dessous donne un exemple d’interface recevant des trames de pause. Le plan d'action consiste à examiner la cause de la congestion dans le périphérique du saut suivant.

GigabitEthernet6/2 is up, line protocol is up

Small Factor Pluggable Optics okay

Hardware is GigMac 4 Port GigabitEthernet, address is 000b.455d.ee02 (bia 000b.455d.ee02)

Description: Cisco Sydney Lab

Internet address is 219.158.33.86/30

MTU 1500 bytes, BW 500000 Kbit, DLY 10 usec, rely 255/255, load 154/255

Encapsulation ARPA, loopback not set

Keepalive set (10 sec)

Full Duplex, 1000Mbps, link type is force-up, media type is LX

output flow-control is on, input flow-control is on

ARP type: ARPA, ARP Timeout 04:00:00

Last input 00:00:02, output 00:00:02, output hang never

Last clearing of "show interface" counters 7w1d

Queueing strategy: random early detection (WRED)

Output queue 0/40, 22713601 drops; input queue 0/75, 736369 drops

Available Bandwidth 224992 kilobits/sec

30 second input rate 309068000 bits/sec, 49414 packets/sec

30 second output rate 303400000 bits/sec, 73826 packets/sec

143009959974 packets input, 88976134206186 bytes, 0 no buffer

Received 7352 broadcasts, 0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored

0 watchdog, 7352 multicast, 45 pause input

234821393504 packets output, 119276570730993 bytes, 0 underruns

Transmitted 73201 broadcasts

0 output errors, 0 collisions, 0 interface resets

0 babbles, 0 late collision, 0 deferred

0 lost carrier, 0 no carrier, 0 pause output

0 output buffer failures, 0 output buffers swapped out

Scénario 3 :

En cas de surabonnement dû à une mauvaise conception du réseau, à des pics de trafic ou à une attaque DOS. Un avertissement de QM Sanity peut se produire si le trafic est élevé et soutenu et que le trafic dirigé vers le routeur est supérieur à ce que les cartes de ligne peuvent gérer.

Pour déterminer la cause de ce problème, vérifiez les débits de trafic sur toutes les interfaces du routeur. Cela permet de savoir si l’une des liaisons haut débit encombre les liaisons lentes.

Utilisez la commande show interface output.

Dépannage des commandes

Pour vérifier le niveau de santé QM actuel d'un LC

-

Attacher à LC

-

Passez en mode enable

-

Exécuter la commande test fab

-

Collecter le résultat de « qm_sanity_info »

-

Option q pour quitter la ligne de commande test fab

-

Quitter LC

Pour configurer les paramètres QM Sanity

- passage en mode de configuration

- Exécutez hw-module slot <slot#> qm-sanity tofab warning freq <>

Pour activer/désactiver les débogages QM sanity

- Attacher à LC

-

Passez en mode enable

-

Exécuter la commande test fab

-

Exécutez «qm_sanity_debug». Exécutez à nouveau et cela arrêtera les débogages

-

Option q pour quitter la ligne de commande test fab

-

Quitter LC

Pour vérifier les statistiques de base de l'interface de matrice GSR

- show controller fia

Pour vérifier les files d'attente Tofab

- show controllers tofab queues

Pour vérifier les files d'attente Frfab

- show controller frfab queues

Exemple :

Le résultat ci-dessous est extrait d’un routeur de travaux pratiques opérationnel pour illustrer les résultats de la commande.

GSR-1-PE-5#show controller fia

Fabric configuration: 10Gbps bandwidth (2.4Gbps available), redundant fabric

Master Scheduler: Slot 17 Backup Scheduler: Slot 16

Fab epoch no 0 Halt count 0

From Fabric FIA Errors

-----------------------

redund overflow 0 cell drops 0

cell parity 0

Switch cards present 0x001F Slots 16 17 18 19 20

Switch cards monitored 0x001F Slots 16 17 18 19 20

Slot: 16 17 18 19 20

Name: csc0 csc1 sfc0 sfc1 sfc2

-------- -------- -------- -------- --------

los 0 0 0 0 0

state Off Off Off Off Off

crc16 0 0 0 0 0

To Fabric FIA Errors

-----------------------

sca not pres 0 req error 0 uni fifo overflow 0

grant parity 0 multi req 0 uni fifo undrflow 0

cntrl parity 0 uni req 0

multi fifo 0 empty dst req 0 handshake error 0

cell parity 0

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_debug

QM Sanity Debug enabled

BFLC (? for help) [qm_sanity_debug]:

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

QM Sanity Debug disabled

BFLC (? for help) [qm_sanity_debug]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 20 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exi

Disconnecting from slot 1.

Connection Duration: 00:01:09

GSR-1-PE-5#config t

Enter configuration commands, one per line. End with CNTL/Z.

GSR-1-PE-5(config)#hw-module slot 1 qm-sanity tofab warning freq 10

GSR-1-PE-5(config)#end

GSR-1-PE-5#attach 1

02:57:25: %SYS-5-CONFIG_I: Configured from console by console

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 10 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exit

Disconnecting from slot 1.

Connection Duration: 00:00:27

GSR-1-PE-5#execute-on all show controllers tofab queues

========= Line Card (Slot 0) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262141/262141 buffers specified/carved

265028848/265028848 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

107232/107232 (buffers specified/carved), 40.90%, 80 byte data size

601 107832 107232 262143

73232/73232 (buffers specified/carved), 27.93%, 608 byte data size

107833 181064 73232 262143

57539/57539 (buffers specified/carved), 21.94%, 1616 byte data size

181065 238603 57539 262143

23538/23538 (buffers specified/carved), 8.97%, 4592 byte data size

238604 262141 23538 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

155 154 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

15 2191(hpr) 0 0 0 0

Multicast 2048 0 0 0 262143

2049 0 0 0 262143

========= Line Card (Slot 1) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: 26000000, carve base: 26010000

268369920 bytes carve size, 4 SDRAM bank(s), 32768 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262140/261472 buffers specified/carved

267790176/264701344 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 601 102601 102001 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 102602 181063 78462 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 181064 238602 57539 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 238603 261472 22870 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

30 85 84 600 262143

Raw Queue (high priority):

27 0 0 0 65368

Raw Queue (medium priority):

28 0 0 0 32684

Raw Queue (low priority):

31 0 0 0 16342

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

=============================================================

::::::::::::::::::::

Hi Priority

0 2176(hpr) 0 0 0

1 2177(hpr) 0 0 0

2 2178(hpr) 0 0 0

3 2179(hpr) 0 0 0

4 2180(hpr) 553 552 0

5 2181(hpr) 0 0 0

6 2182(hpr) 0 0 0

7 2183(hpr) 0 0 0

8 2184(hpr) 0 0 0

9 2185(hpr) 0 0 0

10 2186(hpr) 0 0 0

11 2187(hpr) 0 0 0

12 2188(hpr) 0 0 0

13 2189(hpr) 0 0 0

14 2190(hpr) 0 0 0

15 2191(hpr) 0 0 0

Multicast

2048 0 0 0

2049 0 0 0

2050 0 0 0

2051 0 0 0

2052 0 0 0

2053 0 0 0

2054 0 0 0

2055 0 0 0

========= Line Card (Slot 3) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4112 bytes, min buffer data size 80 bytes

262142/262142 buffers specified/carved

230886224/230886224 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

3 non-IPC free queues:

94155/94155 (buffers specified/carved), 35.91%, 80 byte data size

601 94755 94155 262143

57539/57539 (buffers specified/carved), 21.94%, 608 byte data size

94756 152294 57539 262143

109848/109848 (buffers specified/carved), 41.90%, 1616 byte data size

152295 262142 109848 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

207 206 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

1 0 0 0 262143

2 0 0 0 262143

3 0 0 0 262143

:::::::::::::::::::::::::::

2049 0 0 0 262143

2050 0 0 0 262143

2051 0 0 0 262143

2052 0 0 0 262143

2053 0 0 0 262143

2054 0 0 0 262143

2055 0 0 0 262143

GSR-1-PE-5#execute-on slot 2 show controller frfab queues

========= Line Card (Slot 2) =========

Carve information for FrFab buffers

SDRAM size: 268435456 bytes, address: D0000000, carve base: D241D100

230567680 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

235926/235926 buffers specified/carved

226853664/226853664 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

96484/96484 (buffers specified/carved), 40.89%, 80 byte data size

11598 11597 96484 262143

77658/77658 (buffers specified/carved), 32.91%, 608 byte data size

103116 103115 77658 262143

40005/40005 (buffers specified/carved), 16.95%, 1616 byte data size

178588 178587 40005 262143

21179/21179 (buffers specified/carved), 8.97%, 4592 byte data size

214748 235926 21179 262143

IPC Queue:

600/600 (buffers specified/carved), 0.25%, 4112 byte data size

66 65 600 262143

Multicast Raw Queue:

0 0 0 58981

Multicast Replication Free Queue:

235930 262143 26214 262143

Raw Queue (high priority):

78 77 0 235927

Raw Queue (medium priority):

11596 11595 0 58981

Raw Queue (low priority):

0 0 0 23592

Interface Queues:

Interface Queue# Head Tail Length Threshold

pkts pkts

======================================================

0 0 103107 103106 0 32768

3 178588 178587 0 32768

1 4 103110 103109 0 32768

7 11586 11585 0 32768

2 8 0 0 0 32768

11 0 0 0 32768

3 12 0 0 0 32768

15 0 0 0 32768

GSR-1-PE-5#

Historique de révision

| Révision | Date de publication | Commentaires |

|---|---|---|

1.0 |

30-Jul-2017 |

Première publication |

Contribution d’experts de Cisco

- Shabeer MansoorTAC Cisco

Contacter Cisco

- Ouvrir un dossier d’assistance

- (Un contrat de service de Cisco est requis)

Commentaires

Commentaires