Risoluzione dei problemi "QM_SANITY_WARNING" Message su router serie 12000

Opzioni per il download

Linguaggio senza pregiudizi

La documentazione per questo prodotto è stata redatta cercando di utilizzare un linguaggio senza pregiudizi. Ai fini di questa documentazione, per linguaggio senza di pregiudizi si intende un linguaggio che non implica discriminazioni basate su età, disabilità, genere, identità razziale, identità etnica, orientamento sessuale, status socioeconomico e intersezionalità. Le eventuali eccezioni possono dipendere dal linguaggio codificato nelle interfacce utente del software del prodotto, dal linguaggio utilizzato nella documentazione RFP o dal linguaggio utilizzato in prodotti di terze parti a cui si fa riferimento. Scopri di più sul modo in cui Cisco utilizza il linguaggio inclusivo.

Informazioni su questa traduzione

Cisco ha tradotto questo documento utilizzando una combinazione di tecnologie automatiche e umane per offrire ai nostri utenti in tutto il mondo contenuti di supporto nella propria lingua. Si noti che anche la migliore traduzione automatica non sarà mai accurata come quella fornita da un traduttore professionista. Cisco Systems, Inc. non si assume alcuna responsabilità per l’accuratezza di queste traduzioni e consiglia di consultare sempre il documento originale in inglese (disponibile al link fornito).

Introduzione

Questo documento descrive la procedura per eseguire il debug dei messaggi di esaurimento del buffer di pacchetto che possono verificarsi su diverse schede di linea in un router cisco serie 12000 con IOS. È fin troppo frequente che si verifichino sprechi di tempo e risorse nella sostituzione dell'hardware che funziona correttamente a causa della mancanza di conoscenze sulla gestione dei buffer GSR.

Prerequisiti

Requisiti

Il lettore deve avere una panoramica dell'architettura del router Cisco serie 12000.

Componenti usati

Le informazioni fornite in questo documento si basano sulle seguenti versioni software e hardware:

- Cisco serie 12000 Internet Router

- Software Cisco IOS® con supporto per Gigabit Switch Router

Le informazioni discusse in questo documento fanno riferimento a dispositivi usati in uno specifico ambiente di emulazione. Su tutti i dispositivi menzionati nel documento la configurazione è stata ripristinata ai valori predefiniti. Se la rete è operativa, valutare attentamente eventuali conseguenze derivanti dall'uso dei comandi.

Convenzioni

Per ulteriori informazioni sulle convenzioni usate, consultare il documento Cisco sulle convenzioni nei suggerimenti tecnici.

Problema

I router GSR o serie 12000 cisco hanno un'architettura realmente distribuita. Ciò significa che ciascun LC esegue la propria copia dell'immagine software di Cisco IOS e dispone dell'intelligenza per completare da solo la decisione di inoltro dei pacchetti. Ogni scheda di linea ha le proprie caratteristiche

- Ricerca inoltro

- Gestione del buffer di pacchetto

- QOS

- Controllo del flusso

Una delle operazioni più importanti durante la commutazione dei pacchetti nella GSR è la gestione dei buffer, che viene effettuata da vari buffer Management ASIC (BMA) situati nelle schede di linea. Di seguito vengono riportati alcuni messaggi relativi alla gestione del buffer GSR che potrebbero apparire nei log del router durante la produzione. Nella sezione seguente verranno illustrati i diversi trigger che potrebbero causare la visualizzazione di questi messaggi nei log del router e le azioni correttive da intraprendere per mitigare il problema. In alcune situazioni, questa condizione potrebbe anche causare una perdita dei pacchetti che si manifesta come flap del protocollo e causare un impatto sulla rete.

%EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted

SLOT 1:Sep 16 19:06:40.003 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(1) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:45.943 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(0) are available in ToFab FreeQ pool# 1

SLOT 0:Sep 16 19:06:46.267 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(2) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:47.455 UTC: %EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted. Recarving the ToFab buffers

SLOT 8:Sep 16 19:06:47.471 UTC: %EE192-3-BM_QUIESCE:

Soluzione

Introduzione

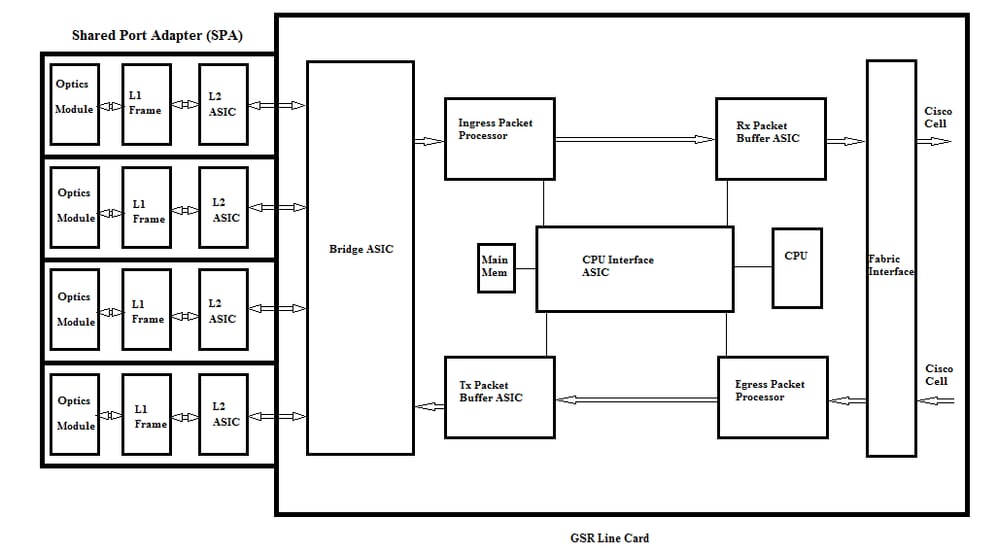

Per risolvere gli errori di avviso QM-SANITY, è necessario conoscere il flusso dei pacchetti su una scheda di linea GSR. La Figura seguente spiega i blocchi principali di una scheda di linea C12k e il percorso del flusso del pacchetto.

La scheda di linea (LC) di un Cisco serie 12000 Internet Router ha due tipi di memoria:

- Memoria di routing o processore (RAM dinamica - DRAM): questa memoria consente principalmente al processore incorporato di eseguire il software Cisco IOS e memorizzare le tabelle di routing di rete (Forwarding Information Base - FIB, adiacenza)

- Memoria pacchetto (Synchronous Dynamic RAM - SDRAM): la memoria del pacchetto della scheda di linea memorizza temporaneamente i pacchetti di dati in attesa di decisioni di commutazione da parte del processore della scheda di linea.

Come si evince dall'immagine precedente, la scheda di linea GSR dispone di un ASIC (Application Specific Integrated Circuit) specifico per il buffer dei pacchetti, uno in ogni direzione del flusso del traffico che fornisce accesso alla memoria del pacchetto. Questi ASIC, noti anche come BMA (Buffer Management ASIC), eseguono il buffering dei pacchetti e la funzione di gestione delle code del buffer sulla scheda di linea. Per supportare alte velocità di throughput/inoltro, la memoria del pacchetto in entrambe le direzioni viene scolpita in pool di memoria di dimensioni diverse progettati per inoltrare pacchetti di MTU di diverse dimensioni.

I frame ricevuti dalle schede PLIM (Physical Layer Interface Module) vengono elaborati al layer 2 e inviati a una memoria locale nella scheda PLIM. Una volta completata l'unità di dati ricevuta, un ASIC nel PLIM contatta il BMA in entrata e richiede un buffer di dimensioni appropriate. Se il buffer viene concesso, il pacchetto viene spostato nella memoria del pacchetto in entrata della scheda di linea. Se non sono disponibili buffer, il pacchetto viene scartato e il contatore di interfaccia ignorato diventa attivo. Il processore di pacchetti in entrata esegue le funzioni di elaborazione sul pacchetto, prende la decisione di inoltro e sposta il pacchetto nella coda toFab corrispondente alla scheda di linea in uscita. L'ASIC (Fabric Interface) (FIA) segmenta il pacchetto alle celle cisco e la cella viene trasmessa al fabric dello switch. I pacchetti vengono quindi ricevuti dal fabric dello switch dalla FIA sulla scheda di linea in uscita e vanno alle code di Frfab dove vengono ricomposti, quindi al PLIM in uscita e infine inviati sul cavo.

La decisione di FrFab BMA di selezionare il buffer da un particolare pool di buffer si basa sulla decisione presa dal motore di commutazione della scheda in entrata. Poiché tutte le code sull'intera scatola sono delle stesse dimensioni e nello stesso ordine, il motore di commutazione indica al LC di trasmissione di posizionare il pacchetto nella stessa coda numerica da cui è entrato nel router.

Mentre il pacchetto viene scambiato, le dimensioni della coda di un particolare pool di buffer nella scheda di linea in entrata utilizzata per spostare il pacchetto diminuiranno di un'unità finché la BMA nella scheda di linea in uscita non restituisce il buffer. In questo caso, è opportuno notare che la gestione completa dei buffer viene effettuata nell'hardware dall'ASIC di gestione dei buffer e per un funzionamento senza errori è necessario che la BMA restituisca i buffer al pool originale da cui è stata originata.

In tre scenari, la gestione del buffer dei pacchetti GSR può causare stress o guasti che possono causare la perdita dei pacchetti. Di seguito sono riportati i tre scenari.

Scenario 1:

Gestione della coda hardware non riuscita. Questo si verifica quando il BMA in uscita non restituisce il buffer del pacchetto o restituisce il buffer del pacchetto a un pool di buffer errato. Se i buffer vengono restituiti al pool errato, alcuni pool di buffer aumentano e alcuni pool di buffer si esauriscono nel corso di un periodo di tempo e alla fine si verificano pacchetti con dimensioni del pool di buffer insufficienti. Inizieremo a vedere gli avvisi QM-Sanity quando il buffer del pacchetto si esaurisce e supera la soglia di avviso.

Usare il comando QM Sanity Debug e show controllers to fab Queues per verificare se questa condizione ha effetto. Per informazioni su come abilitare le soglie di integrità QM, consultare la sezione Risoluzione dei problemi.

Questa condizione è generalmente causata da hardware difettoso. Controllare le uscite seguenti sul router e cercare eventuali errori di parità o arresti anomali della scheda di linea. Il rimedio consiste nel sostituire la scheda di linea.

show controllers fia

show context all

show log

Esempio:

Dai debug di integrità QM e dalla coda show controller to fab è possibile verificare che le dimensioni del pool 2 aumentano mentre il pool 4 è in esaurimento. Ciò indica che il pool 4 sta perdendo i buffer e viene restituito al pool 2.

Debug QM:

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 1: Carve Size 102001: Current Size 73078

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 2: Carve Size 78462: Current Size 181569

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 3: Carve Size 57539: Current Size 6160

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 4: Carve Size 22870: Current Size 67

SLOT 5:Oct 25 04:41:03.286 UTC: IPC FreeQ: Carve Size 600: Current Size 600

show controllers to fab queue (visualizza i controller nelle code di fax):

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 13542 13448 73078 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 131784 131833 181569 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 184620 182591 6160 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 239113 238805 67 262143

Scenario 2:

Congestione del traffico sul dispositivo dell'hop successivo o sul percorso di inoltro. In questo scenario, il dispositivo verso cui il GSR alimenta il traffico non può elaborare alla velocità del GSR e, di conseguenza, il dispositivo dell'hop successivo invia frame di pausa verso il GSR per chiedergli di rallentare. Se il controllo del flusso è abilitato sulle schede GSR PLIM, il router rispetta i frame di pausa e inizia a memorizzare i pacchetti nel buffer. Infine, il router esaurirà i buffer causando la perdita dei messaggi di errore QM Sanity e dei pacchetti. Inizieremo a vedere gli avvisi QM-Sanity quando il buffer del pacchetto si esaurisce e supera la soglia di avviso. Fare riferimento alla sezione sulla risoluzione dei problemi per trovare le soglie di integrità QM.

Usare l'output show interface sull'interfaccia in uscita per verificare se il router è interessato da questo scenario. L'immagine seguente mostra un esempio di interfaccia che riceve i frame di pausa. Il piano d'azione esaminerà la causa della congestione nel dispositivo dell'hop successivo.

GigabitEthernet6/2 is up, line protocol is up

Small Factor Pluggable Optics okay

Hardware is GigMac 4 Port GigabitEthernet, address is 000b.455d.ee02 (bia 000b.455d.ee02)

Description: Cisco Sydney Lab

Internet address is 219.158.33.86/30

MTU 1500 bytes, BW 500000 Kbit, DLY 10 usec, rely 255/255, load 154/255

Encapsulation ARPA, loopback not set

Keepalive set (10 sec)

Full Duplex, 1000Mbps, link type is force-up, media type is LX

output flow-control is on, input flow-control is on

ARP type: ARPA, ARP Timeout 04:00:00

Last input 00:00:02, output 00:00:02, output hang never

Last clearing of "show interface" counters 7w1d

Queueing strategy: random early detection (WRED)

Output queue 0/40, 22713601 drops; input queue 0/75, 736369 drops

Available Bandwidth 224992 kilobits/sec

30 second input rate 309068000 bits/sec, 49414 packets/sec

30 second output rate 303400000 bits/sec, 73826 packets/sec

143009959974 packets input, 88976134206186 bytes, 0 no buffer

Received 7352 broadcasts, 0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored

0 watchdog, 7352 multicast, 45 pause input

234821393504 packets output, 119276570730993 bytes, 0 underruns

Transmitted 73201 broadcasts

0 output errors, 0 collisions, 0 interface resets

0 babbles, 0 late collision, 0 deferred

0 lost carrier, 0 no carrier, 0 pause output

0 output buffer failures, 0 output buffers swapped out

Scenario 3:

In momenti di sovrascrittura a causa di progettazione della rete inadeguata/picchi di traffico/attacchi DOS. L'avviso di integrità QM può verificarsi in caso di traffico elevato e prolungato, quando al router viene indirizzato più traffico di quello che le schede di linea possono gestire.

Per risolvere la causa, controllare le velocità del traffico su tutte le interfacce del router. Ciò rivelerà se uno dei collegamenti ad alta velocità sono congestionanti collegamenti lenti.

Usare il comando show interface output.

Comandi per la risoluzione dei problemi

Per controllare il livello di integrità QM corrente per un LC

-

Collega a LC

-

Vai alla modalità di abilitazione

-

Esegui comando test fab

-

Raccogli l'output di "qm_sanity_info"

-

Opzione q per uscire dalla riga di comando di test fab

-

Esci da LC

Per configurare i parametri di integrità QM

- passa alla modalità di configurazione

- Eseguire il comando hw-module slot <slot#> qm-sanity to fab warning freq <>

Per abilitare/disabilitare i debug di integrità QM

- Collega a LC

-

Vai alla modalità di abilitazione

-

Esegui comando test fab

-

Eseguire "qm_sanity_debug". Esegui di nuovo e interromperà i debug

-

Opzione q per uscire dalla riga di comando di test fab

-

Esci da LC

Per controllare le statistiche di base dell'interfaccia GSR

- show controller

Per controllare le code Tofab

- mostra i controller alle code di fax

Per controllare le code Frfab

- mostra code frfab controller

Esempio:

L'output seguente viene estratto da un router Lab funzionante per dimostrare gli output del comando.

GSR-1-PE-5#show controller fia

Fabric configuration: 10Gbps bandwidth (2.4Gbps available), redundant fabric

Master Scheduler: Slot 17 Backup Scheduler: Slot 16

Fab epoch no 0 Halt count 0

From Fabric FIA Errors

-----------------------

redund overflow 0 cell drops 0

cell parity 0

Switch cards present 0x001F Slots 16 17 18 19 20

Switch cards monitored 0x001F Slots 16 17 18 19 20

Slot: 16 17 18 19 20

Name: csc0 csc1 sfc0 sfc1 sfc2

-------- -------- -------- -------- --------

los 0 0 0 0 0

state Off Off Off Off Off

crc16 0 0 0 0 0

To Fabric FIA Errors

-----------------------

sca not pres 0 req error 0 uni fifo overflow 0

grant parity 0 multi req 0 uni fifo undrflow 0

cntrl parity 0 uni req 0

multi fifo 0 empty dst req 0 handshake error 0

cell parity 0

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_debug

QM Sanity Debug enabled

BFLC (? for help) [qm_sanity_debug]:

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

QM Sanity Debug disabled

BFLC (? for help) [qm_sanity_debug]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 20 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exi

Disconnecting from slot 1.

Connection Duration: 00:01:09

GSR-1-PE-5#config t

Enter configuration commands, one per line. End with CNTL/Z.

GSR-1-PE-5(config)#hw-module slot 1 qm-sanity tofab warning freq 10

GSR-1-PE-5(config)#end

GSR-1-PE-5#attach 1

02:57:25: %SYS-5-CONFIG_I: Configured from console by console

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 10 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exit

Disconnecting from slot 1.

Connection Duration: 00:00:27

GSR-1-PE-5#execute-on all show controllers tofab queues

========= Line Card (Slot 0) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262141/262141 buffers specified/carved

265028848/265028848 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

107232/107232 (buffers specified/carved), 40.90%, 80 byte data size

601 107832 107232 262143

73232/73232 (buffers specified/carved), 27.93%, 608 byte data size

107833 181064 73232 262143

57539/57539 (buffers specified/carved), 21.94%, 1616 byte data size

181065 238603 57539 262143

23538/23538 (buffers specified/carved), 8.97%, 4592 byte data size

238604 262141 23538 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

155 154 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

15 2191(hpr) 0 0 0 0

Multicast 2048 0 0 0 262143

2049 0 0 0 262143

========= Line Card (Slot 1) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: 26000000, carve base: 26010000

268369920 bytes carve size, 4 SDRAM bank(s), 32768 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262140/261472 buffers specified/carved

267790176/264701344 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 601 102601 102001 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 102602 181063 78462 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 181064 238602 57539 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 238603 261472 22870 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

30 85 84 600 262143

Raw Queue (high priority):

27 0 0 0 65368

Raw Queue (medium priority):

28 0 0 0 32684

Raw Queue (low priority):

31 0 0 0 16342

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

=============================================================

::::::::::::::::::::

Hi Priority

0 2176(hpr) 0 0 0

1 2177(hpr) 0 0 0

2 2178(hpr) 0 0 0

3 2179(hpr) 0 0 0

4 2180(hpr) 553 552 0

5 2181(hpr) 0 0 0

6 2182(hpr) 0 0 0

7 2183(hpr) 0 0 0

8 2184(hpr) 0 0 0

9 2185(hpr) 0 0 0

10 2186(hpr) 0 0 0

11 2187(hpr) 0 0 0

12 2188(hpr) 0 0 0

13 2189(hpr) 0 0 0

14 2190(hpr) 0 0 0

15 2191(hpr) 0 0 0

Multicast

2048 0 0 0

2049 0 0 0

2050 0 0 0

2051 0 0 0

2052 0 0 0

2053 0 0 0

2054 0 0 0

2055 0 0 0

========= Line Card (Slot 3) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4112 bytes, min buffer data size 80 bytes

262142/262142 buffers specified/carved

230886224/230886224 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

3 non-IPC free queues:

94155/94155 (buffers specified/carved), 35.91%, 80 byte data size

601 94755 94155 262143

57539/57539 (buffers specified/carved), 21.94%, 608 byte data size

94756 152294 57539 262143

109848/109848 (buffers specified/carved), 41.90%, 1616 byte data size

152295 262142 109848 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

207 206 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

1 0 0 0 262143

2 0 0 0 262143

3 0 0 0 262143

:::::::::::::::::::::::::::

2049 0 0 0 262143

2050 0 0 0 262143

2051 0 0 0 262143

2052 0 0 0 262143

2053 0 0 0 262143

2054 0 0 0 262143

2055 0 0 0 262143

GSR-1-PE-5#execute-on slot 2 show controller frfab queues

========= Line Card (Slot 2) =========

Carve information for FrFab buffers

SDRAM size: 268435456 bytes, address: D0000000, carve base: D241D100

230567680 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

235926/235926 buffers specified/carved

226853664/226853664 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

96484/96484 (buffers specified/carved), 40.89%, 80 byte data size

11598 11597 96484 262143

77658/77658 (buffers specified/carved), 32.91%, 608 byte data size

103116 103115 77658 262143

40005/40005 (buffers specified/carved), 16.95%, 1616 byte data size

178588 178587 40005 262143

21179/21179 (buffers specified/carved), 8.97%, 4592 byte data size

214748 235926 21179 262143

IPC Queue:

600/600 (buffers specified/carved), 0.25%, 4112 byte data size

66 65 600 262143

Multicast Raw Queue:

0 0 0 58981

Multicast Replication Free Queue:

235930 262143 26214 262143

Raw Queue (high priority):

78 77 0 235927

Raw Queue (medium priority):

11596 11595 0 58981

Raw Queue (low priority):

0 0 0 23592

Interface Queues:

Interface Queue# Head Tail Length Threshold

pkts pkts

======================================================

0 0 103107 103106 0 32768

3 178588 178587 0 32768

1 4 103110 103109 0 32768

7 11586 11585 0 32768

2 8 0 0 0 32768

11 0 0 0 32768

3 12 0 0 0 32768

15 0 0 0 32768

GSR-1-PE-5#

Cronologia delle revisioni

| Revisione | Data di pubblicazione | Commenti |

|---|---|---|

1.0 |

30-Jul-2017 |

Versione iniziale |

Contributo dei tecnici Cisco

- Shabeer MansoorCisco TAC

Feedback

Feedback