- Preface

- Using Cisco IOS XE Software

- SIP and SPA Product Overview

- Overview of the SIP

- Configuring the SIP

- Troubleshooting the SIP

- Overview of the ATM SPAs

- Configuring the ATM SPAs

- Troubleshooting the ATM SPAs

- Overview of the Ethernet SPAs

- Configuring the Ethernet SPAs

- Troubleshooting the Gigabit Ethernet SPAs

- Overview of the POS SPAs

- Configuring the POS SPAs

- Overview of the Serial SPAs

- Configuring the 8-Port Channelized T1/E1 Serial SPA

- Configuring the 2-Port and 4-Port Channelized T3 SPAs

- Configuring the 2-Port and 4-Port T3/E3 Serial SPA

- Configuring the 4-Port Serial Interface SPA

- Configuring the 1-Port Channelized OC-3/STM-1 SPA and 1-Port Channelized OC-12/STM-4 SPA

- Troubleshooting the Serial SPAs

- Overview of the Cisco WebEx Node for the Cisco ASR 1000 Series Routers

- Configuring the Cisco WebEx Node for the ASR 1000 Series Aggregation Services Routers

- Troubleshooting the Cisco WebEx Node for the ASR 1000 Series Aggregation Services Routers

- Overview of the Cisco DSP SPA for the ASR 1000 Series Aggregation Services Routers

- Configuring the Cisco DSP SPA for the ASR 1000 Series Aggregation Services Routers

- Upgrading Field-Programmable Devices

- Classifying and Scheduling Packets for the ASR 1000 Series Aggregation Services Routers

- Overview of the Circuit Emulation over Packet Shared Port Adapter

- Configuring the Circuit Emulation over Packet Shared Port Adapter

- Index

Overview of the POS SPAs

This chapter provides information about release history, feature, and MIB support for the Packet over SONET (POS) SPAs on Cisco ASR 1000 Series Aggregation Services Routers. This chapter includes the following sections:

- Release History

- POS Technology Overview

- Supported Features

- Restrictions

- Supported MIBs

- SPA Architecture

- Displaying the SPA Hardware Type

Release History

The following table lists the release history for the Packet over SONET (POS) SPAs on Cisco ASR 1000 Series Aggregation Services Routers:

|

Release |

Modification |

|---|---|

|

Cisco IOS XE Release 3.11 |

The restrictions for 1 port OC-48 POS/RPR SPA were updated. |

|

Cisco IOS XE Release 3.10 |

Support for the 4-Port OC-3c/STM-1 POS SPA version 2 was introduced on the Cisco ASR 1000 Series Aggregation Services Routers. |

|

Cisco IOS XE Release 2.4 |

Support for the following SPAs was introduced on the Cisco ASR 1000 Series Aggregation Services Routers:

|

|

Cisco IOS XE Release 2.2 |

Support for the following SPAs was introduced on the Cisco ASR 1000 Series Aggregation Services Routers:

|

|

Cisco IOS XE Release 2.1 |

Support for the following SPAs was introduced on the Cisco ASR 1000 Series Aggregation Services Routers:

|

POS Technology Overview

Packet-over-SONET is a high-speed method of transporting IP traffic between two points. This technology combines the Point-to-Point Protocol (PPP), High-level Data Link Control (HDLC), or Frame Relay with Synchronous Optical Network (SONET) and Synchronous Digital Hierarchy (SDH) interfaces.

SONET is an octet-synchronous multiplex scheme defined by the American National Standards Institute (ANSI) standard (T1.1051988) for optical digital transmission at hierarchical rates from 51.840 Mbps to 9.95 Gbps (Synchronous Transport Signal, STS-1 to STS-48) and greater. SDH is an equivalent international standard for optical digital transmission at hierarchical rates from 155.520 Mbps (Synchronous Transfer Mode-1 [STM-1]) to 9.95 Gbps (STM-16) and greater.

SONET specifications have been defined for single-mode fiber and multimode fiber. The POS SPAs allow transmission over single-mode and multimode optical fiber at Optical Carrier 3, 12, 48, and 192 (OC-3, OC-12, OC-48, and OC-192) rates.

SONET/SDH transmission rates are integral multiples of 51.840 Mbps. The following transmission multiples are currently specified and used on the POS SPAs on the Cisco ASR 1000 Series Aggregation Services Routers:

- OC-3c/STM-1—155.520 Mbps

- OC-12c/STM-4—622.080 Mbps

- OC-48c/STM-16—2.488 Gbps

- OC-192/STM-64 XFP—9.95 Gbps

Supported Features

The following features are supported for Packet over SONET (POS) SPAs on Cisco ASR 1000 Series Aggregation Services Routers:

- Small form-factor pluggable (SFP) and XFP optics module OIR

- Field-programmable gate array (FPGA) upgrade support

- IPv4 and IPv6 addressing

- SONET/SDH Compliance Features

- SONET/SDH Error, Alarm, and Performance Monitoring Features

- SONET/SDH Synchronization Features

- WAN Protocol Features

- Network Management Features

SONET/SDH Compliance Features

The Compliance features supported for the Packet over SONET (POS) SPAs on Cisco ASR 1000 Series Aggregation Services Routers are as follows:

- American National Standards Institute (ANSI) T1.105

- ITU-T G.707, G.783, G.957, G.958

- Telcordia GR-253-CORE: SONET Transport Systems: Common Generic Criteria

- Telcordia GR-1244: Clocks for the Synchronized Network: Common Generic Criteria

SONET/SDH Error, Alarm, and Performance Monitoring Features

The performance monitoring features for the Packet over SONET (POS) SPAs on Cisco ASR 1000 Series Aggregation Services Routers are as follows:

- Signal failure bit error rate (SF-BER)

- Signal degrade bit error rate (SD-BER)

- Signal label payload construction (C2)

- Path trace byte (J1)

- Section Loss of signal (LOS)

- Section Loss of frame (LOF)

- Section Error counts for B1

- Section Threshold crossing alarms (TCA) for B1

- Line alarm indication signal (LAIS)

- Line remote defect indication (LRDI)

- Line remote error indication (LREI)

- Line Error counts for B2

- Line Threshold crossing alarms (TCA) for B2

- Path alarm indication signal (PAIS)

- Path remote defect indication (PRDI)

- Path remote error indication (PREI)

- Path Error counts for B3

- Path Threshold crossing alarms (TCA) for B3

- Path Loss of pointer (LOP)

- Path New pointer events (NEWPTR)

- Path Positive stuffing event (PSE)

- Path Negative stuffing event (NSE)

SONET/SDH Synchronization Features

The SONET/SDH synchronization features for the Packet over SONET (POS) SPAs on Cisco ASR 1000 Series Aggregation Services Routers:

- Local (internal) timing (for inter-router connections over dark fiber or Wavelength Division Multiplex [WDM] equipment)

- Loop (line) timing (for connecting to SONET/SDH equipment)

- Approximately 20 ppm clock accuracy over the full range of the operating temperature

WAN Protocol Features

- HDLC and Frame Relay IETF encapsulation

- Multiprotocol Label Switching (MPLS)

- RFC 1661, The Point-to-Point Protocol (PPP)

- RFC 1662, PPP in HDLC framing

- RFC 2615, PPP over SONET/SDH (with 1+x43 self-synchronous payload scrambling)

Network Management Features

- Simple Network Management Protocol (SNMP) Management Information Base (MIB) counters

- Local (diagnostic) loopback

- Network loopback

- NetFlow Data Export

-

RFC 3592 performance statistics for timed intervals (current, 15-minute, multiple 15-minute, and 1-day intervals):

- Section CV (code violations)

- Section ES (errored seconds)

- Section SES (severely errored seconds)

- Near end & Far end Line CV

- Near end & Far end Line ES

- Near end & Far end Line SES

- Near end & Far end Line UAS (unavailable seconds)

- Near end & Far end Path CV

- Near end & Far end Path ES

- Near end & Far end Path SES

- Near end & Far end Path UAS

Restrictions

The following table provides information about POS feature compatibility and restrictions by SIP and SPA combination. For SIP-specific features and restrictions see Overview of SIP .

|

Feature |

Cisco ASR1000-SIP10 |

|---|---|

|

Bridge Control Protocol (BCP) |

Not supported on any POS SPAs. |

|

Dynamic Packet Transport (DPT), which includes RPR/SRP |

Not supported on any POS SPAs. |

|

Frame Relay |

Supported on all POS SPAs. |

The followings are the restrictions for 1-port OC-48 POS/RPR SPA

- Line Remote Error Indication (LREI) and Path Remote Error Indication (PREI) alarms are not reported on the 1-port OC-48 POS/RPR SPA.

Supported MIBs

The following MIBs are supported for the POS SPAs on the Cisco ASR 1000 Series Routers:

- CISCO-ENTITY-ASSET-MIB

- CISCO-ENTITY-FRU-CONTROL-MIB

- CISCO-ENVMON-MIB (For NPEs, NSEs, line cards, and MSCs only)

- CISCO-EXTENDED-ENTITY-MIB

- CISCO-OPTICAL-MIB

- ENTITY-MIB

- OLD-CISCO-CHASSIS-MIB

- IF-MIB

- SONET-MIB (RFC 2558, Definitions of Managed Objects for SONET/SDH Interface Type )

- MIB II

To locate and download MIBs for selected platforms, Cisco IOS releases, and feature sets, use Cisco MIB Locator found at the following URL:

http://tools.cisco.com/ITDIT/MIBS/servlet/index

If Cisco MIB Locator does not support the MIB information that you need, you can also obtain a list of supported MIBs and download MIBs from the Cisco MIBs page at the following URL:

http://www.cisco.com/public/sw-center/netmgmt/cmtk/mibs.shtml

To access Cisco MIB Locator, you must have an account on Cisco.com. If you have forgotten or lost your account information, send a blank e-mail to cco-locksmith@cisco.com. An automatic check will verify that your e-mail address is registered with Cisco.com. If the check is successful, account details with a new random password will be e-mailed to you. Qualified users can establish an account on Cisco.com by following the directions found at this URL:

https://tools.cisco.com/RPF/register/register.do

SPA Architecture

This section provides an overview of the architecture of the POS SPAs and describes the path of a packet in the ingress and egress directions. Some of these areas of the architecture are referenced in the SPA software and can be helpful to understand when troubleshooting or interpreting some of the SPA CLI and show command output.

- 4-Port OC-3c/STM-1 POS SPA Architecture

- 2-Port OC-48c/STM-16 POS SPA Architecture

- 1-Port OC-192c/STM-64 POS/RPR XFP SPA Architecture

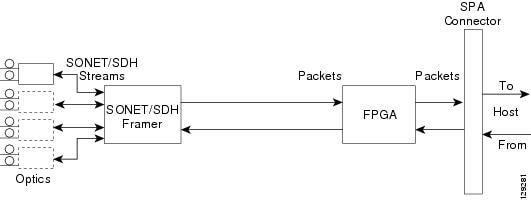

4-Port OC-3c/STM-1 POS SPA Architecture

The following figure identifies some of the hardware devices that are part of the POS SPA architecture. The figure shows the four ports that are supported by the 4-Port OC-3c/STM-1 POS SPA only.

Every incoming and outgoing packet on the 4-Port OC-3c/STM-1 POS SPA goes through the SONET/SDH framer and field-programmable gate array (FPGA) devices.

Path of a Packet in the Ingress Direction

The following steps describe the path of an ingress packet through the 4-Port OC-3c/STM-1 POS SPA:

- The framer receives SONET/SDH streams from the SFP optics, extracts clocking and data, and processes the section, line, and path overhead.

- The framer extracts the POS frame payload and verifies the frame size and frame check sequence (FCS).

- The framer passes valid frames to the field-programmable gate array (FPGA) on the SPA.

- The FPGA on the SPA transfers frames to the host through the SPI4.2 bus for further processing and switching.

Path of a Packet in the Egress Direction

The following steps describe the path of an egress packet through the 4-Port OC-3c/STM-1 POS SPA:

- The host sends packets to the FPGA on the SPA using the SPI4.2 bus.

- The FPGA on the SPA stores the data in the appropriate channel first-in first-out (FIFO) queue.

- The FPGA on the SPA passes the packet to the framer.

- The framer accepts the data and stores it in the appropriate channel queue.

- The framer adds the FCS and SONET/SDH overhead.

The framer sends the data to the SFP optics for transmission onto the network.

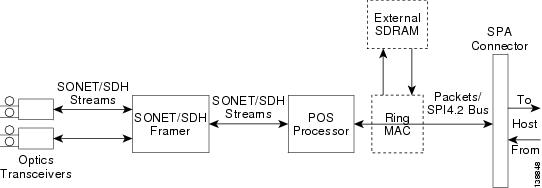

2-Port OC-48c/STM-16 POS SPA Architecture

The following figure identifies the primary hardware devices that are part of the 2-Port OC-48c/STM-16 POS SPA architecture.

Path of a Packet in the Ingress Direction

The following steps describe the path of an ingress packet through the 2-Port OC-48c/STM-16 POS SPA:

- The framer receives SONET/SDH streams from the SFP optics, extracts clocking and data, and processes the section, line, and path overhead.

- The framer detects Loss of Signal (LOS), Loss of Frame (LOF), Severely Errored Frame (SEF), Line Alarm Indication Signal (AIS-L), Loss of Pointer (LOP), Line Remote Defect Indication Signal (Enhanced RDI-L), Path Alarm Indication Signal (AIS-P), Standard and Enhanced Path Remote Defect Indication Signal (RDI-P), Path Remote Error Indication (Enhanced REI-P). The framer extracts or inserts DCC bytes.

- The framer processes the S1 synchronization status byte, the pointer action bytes (per Telcordia GR-253-CORE), and extracts or inserts DCC bytes.

- The POS processor extracts the POS frame payload and verifies the frame size and frame check sequence (FCS).

- The POS processor supports PPP, Frame Relay, or HDLC modes and optionally performs payload scrambling.

- The POS processor passes valid frames to the System Packet Level Interface 4.2 (SPI4.2) interface on the SPA.

- The SPI4.2 interface transfers frames to the host through the SPI4.2 bus for further processing and switching.

Path of a Packet in the Egress Direction

The following steps describe the path of an egress packet through the 2-Port OC-48c/STM-16 POS SPA:

- The host sends packets to the SPA using the SPI4.2 bus.

- The SPA stores the data in the appropriate SPI4 channel’s first-in first-out (FIFO) queue.

- The SPA passes the packet from the SPI4 interface to the POS processor where it is encapsulated in a POS frame and FCS is added.

- The POS frame is sent to the SONET/SDH framer where it is placed into the SONET payload.

- The framer adds the FCS and SONET/SDH overhead.

- The framer sends the data to the SFP optics for transmission onto the network.

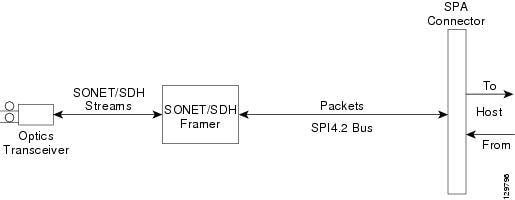

1-Port OC-192c/STM-64 POS/RPR XFP SPA Architecture

The following figure identifies the primary hardware devices that are part of the POS SPA architecture. The figure shows a single optics transceiver. The 1-Port OC-192c/STM-64 POS/RPR XFP SPA supports XFP optics.

In POS mode, every incoming and outgoing packet on the OC-192 POS SPAs goes through the SONET/SDH framer and SPI4.2 interface.

Path of a Packet in the Ingress Direction

The following steps describe the path of an ingress packet through the 1-Port OC-192c/STM-64 POS/RPR XFP SPA:

- The framer receives SONET/SDH streams from the XFP optics, extracts clocking and data, and processes the section, line, and path overhead.

- The framer extracts the POS frame payload and verifies the frame size and frame check sequence (FCS).

- The framer passes valid frames to the System Packet Level Interface 4.2 (SPI4.2) interface on the SPA.

- The SPI4.2 interface transfers frames to the host through the SPI4.2 bus for further processing and switching.

Path of a Packet in the Egress Direction

The following steps describe the path of an egress packet through the 1-Port OC-192c/STM-64 POS/RPR XFP SPA:

- The host sends packets to the SPA using the SPI4.2 bus.

- The SPA stores the data in the appropriate channel’s first-in first-out (FIFO) queue.

- The SPA passes the packet to the framer.

- The framer accepts the data and stores it in the appropriate channel queue.

- The framer adds the FCS and SONET/SDH overhead.

- The framer sends the data to the XFP optics for transmission onto the network.

Displaying the SPA Hardware Type

To verify information about the SPA hardware that is installed in your Cisco ASR 1000 Series Aggregation Services Routers, you can use the show interfaces command or the show controllers command. There are several other commands on the Cisco ASR 1000 Series Aggregation Services Routers that also provide SPA hardware information.

The following table shows the hardware description that appears in the show command output for each POS SPA that is supported on Cisco ASR 1000 Series Aggregation Services Routers.

|

SPA |

Description in show interfaces command |

|---|---|

|

2-Port OC-3c/STM-1 POS SPA |

Hardware is Packet over Sonet |

|

4-Port OC-3c/STM-1 POS SPA |

Hardware is Packet over Sonet |

|

8-Port OC-3c/STM-1 POS SPA |

Hardware is Packet over Sonet |

|

1-Port OC-12c/STM-4 POS SPA |

Hardware is Packet over Sonet |

|

2-Port OC-12c/STM-4 POS SPA |

Hardware is Packet over Sonet |

|

4-Port OC-12c/STM-4 POS SPA |

Hardware is Packet over Sonet |

|

8-Port OC-12c/STM-4 POS SPA |

Hardware is Packet over Sonet |

|

1-Port OC-48c/STM-16 POS SPA |

Hardware is Packet over Sonet |

|

2-Port OC-48c/STM-16 POS/RPR SPA |

Hardware is Packet over Sonet |

|

4-Port OC-48c/STM-16 POS/RPR SPA |

Hardware is Packet over Sonet |

|

1-Port OC-192 POS-XFP SPA |

SPA-OC192POS-XFP |

Example of the show interfaces Command

The following example shows an output of the show interfaces pos command on Cisco ASR 1000 Series Aggregation Services Routers with a 1-Port OC-192c/STM-64 POS/RPR XFP SPA installed in slot 1:

Router# show interfaces POS1/0/0

POS1/0/0 is up, line protocol is up

Hardware is SPA-OC192POS-XFP

MTU 4470 bytes, BW 9952000 Kbit, DLY 100 usec,

reliability 255/255, txload 1/255, rxload 1/255

Encapsulation HDLC, crc 16, loopback not set

Keepalive set (10 sec)

Scramble disabled

Last input 00:00:00, output 00:00:00, output hang never

Last clearing of ''show interface'' counters never

Input queue: 0/375/0/0 (size/max/drops/flushes); Total output drops: 0

Queueing strategy: fifo

Output queue: 0/40 (size/max)

5 minute input rate 0 bits/sec, 0 packets/sec

5 minute output rate 0 bits/sec, 0 packets/sec

138525 packets input, 3324600 bytes, 0 no buffer

Received 0 broadcasts (0 IP multicasts)

1 runts, 6 giants, 0 throttles

0 parity

3951 input errors, 3944 CRC, 0 frame, 0 overrun, 0 ignored, 0 abort

138522 packets output, 3324528 bytes, 0 underruns

0 output errors, 0 applique, 1 interface resets

0 output buffer failures, 0 output buffers swapped out

1 carrier transitions

Example of the show controllers Command

The following example shows an output of the show controllers pos command on Cisco ASR 1000 Series Routers with a 4-Port OC-3c/STM-1 POS SPA installed in slot 1:

Router# show controllers pos 1/0/1 POS1/0/1 SECTION LOF = 0 LOS = 0 BIP(B1) = 0 LINE AIS = 0 RDI = 0 FEBE = 0 BIP(B2) = 0 PATH AIS = 0 RDI = 0 FEBE = 0 BIP(B3) = 0 LOP = 0 NEWPTR = 0 PSE = 0 NSE = 0 Active Defects: None Active Alarms: None Alarm reporting enabled for: SF SLOS SLOF B1-TCA B2-TCA PLOP B3-TCA BER thresholds: SF = 10e-3, SD = 10e-6 TCA thresholds: B1 = 10e-6, B2 = 10e-6, B3 = 10e-6 APS COAPS = 0 PSBF = 0 State: PSBF_state = False Rx(K1/K2): 00/00 Tx(K1/K2): 00/00 S1S0 = 00, C2 = CF CLOCK RECOVERY RDOOL = 0 State: RDOOL_state = False PATH TRACE BUFFER: STABLE Remote hostname: c7600-1 Remote interface: POS7/1/3 Remote IP addr: 10.5.5.4 Remote Rx(K1/K2): 00/00 Tx(K1/K2): 00/00 BER thresholds: SF = 10e-3 SD = 10e-6 TCA thresholds: B1 = 10e-6 B2 = 10e-6 B3 = 10e-6 Clock source: internal

The following example shows output from the show controllers pos pm command on Cisco ASR 1000 Series Aggregation Services Routers with a 2-Port OC-3c/STM-1 POS SPA installed in slot 0:

Router# show controllers pos pm

POS0/1/0

Medium is SONET

Line coding is RZ, Line type is LONG MM

Data in current interval (594 seconds elapsed)

SECTION (NO DEFECT)

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Sev Err Framing Secs

LINE ( NO DEFECT )

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

FAR END LINE

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

PATH ( NO DEFECT )

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

FAR END PATH

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

Total Data (0 valid intervals)

SECTION TOTAL

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Sev Err Framing Secs

LINE TOTAL

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

FAR END LINE TOTAL

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

PATH TOTAL

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

FAR END PATH TOTAL

0 Errored Secs, 0 Severely Err Secs

0 Coding Violations, 0 Unavailabe Secs

Feedback

Feedback